# AWR294x 内存带宽测试及优化方法

Allen Yin China Central FAE

### 摘要

TI 在 2021 年推出的第二代高性能毫米波雷达单芯片 AWR2943 和 AWR2944, 和第一代毫米波雷达芯片 AWR1843 相比性能显著提高,在基于 AWR294x 开发的毫米波雷达的产品中,因为数据访问的量比较大,内存读写的效率直接关系到是否能够在需求时间内完成数据的处理,本文对 AWR294x 片上 MSS 以及 DSS 的内存系统进行读写带宽测试,基于这些结果,介绍了如何在 AWR294x 工程中对内存读写效率进行优化,同时 AM273x 系列 MCU 处理器亦可作为参考。

#### 修改记录

| Version | Date          | Author    | Notes         |  |  |

|---------|---------------|-----------|---------------|--|--|

| 1.0     | Jan 24th 2024 | Allen Yin | First release |  |  |

|         |               |           |               |  |  |

## 目录

| 摘要  |                          |   |

|-----|--------------------------|---|

| 1.  | AWR2943/2944 介绍          | 3 |

| 2.  | AWR294x 内存系统             | 3 |

| 3.  | MSS 模块内存带宽测试及优化          | 5 |

| 4.  | DSS 模块内存带宽测试及优化          | 7 |

| 5.  | 总结                       | 9 |

| 参考  | 文献                       |   |

| _ • |                          |   |

|     |                          |   |

|     |                          |   |

|     | 图                        |   |

|     |                          |   |

|     | . AWR2943/4 和 AWR1843 对比 |   |

|     | AWR294x 内存系统总线互联拓扑图      |   |

|     | . MSS 内存总线系统             |   |

| 图 4 | . DSS 内存总线系统             | 7 |

| 图 5 | . IDMA 使用方法示例            | 9 |

|     |                          |   |

|     | 表                        |   |

| 表 1 | . AWR294x 内存系统容量         | 1 |

| •   | . MSS R5F 数据访问速率         |   |

|     | . MSS EDMA 数据访问速率        |   |

|     | . MSS EDMA               |   |

|     | . DSS DSP                |   |

|     |                          |   |

|     | . DSS EDMA 并发数据访问速率      |   |

| 表 7 | . DSS IDMA 数据访问速率        | 8 |

#### 1. AWR2943/2944 介绍

汽车高级驾驶辅助系统(Advanced Driving Assistance System,ADAS)是利用各种传感器(毫米波雷达、激光雷达、摄像头以及卫星导航),在汽车行驶过程中随时感知周边环境,进行障碍物体的识别与追踪,通过系统运算分析提供给驾驶员辅助决策信息。其中毫米波雷达具有全天候优秀的测距测速性能,抗干扰能力,在 ADAS 系统内得到了广泛应用。

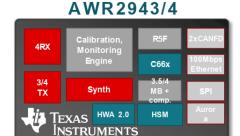

TI 基于 RF-CMOS 工艺将毫米波雷达数据链路的中射频电路,VCO,ADC 和 MCU,DSP 集成在单颗芯片内,极大降低了汽车雷达的成本和开发难度,众多用户在 AWR1642/1843 上开发并量产了毫米波雷达产品。 随着 ADAS 系统的成熟和推广,用户对下一代雷达的性能的要求比第一代毫米波雷达芯片 AWR1642/1843 的基础上有成倍提高,因此,TI 在 2021 年推出的第二代高性能毫米波雷达单芯片 AWR2943 和 AWR2944,和第一代毫米波雷达芯片 AWR1843 相比性能显著提高,具体的增强如图 1 所示:

- 200MHz ARM-R4F MCU

- √ 1.75x 3.5x (Dual core mode) enhancement in MCU MIPS

- · 2MB on-chip RAM

- ✓ 2x Increase in on-chip RAM

- HWA1.0 @200MHz

- √ HWA2.0 1.5x performance enhancements w/ radar pre-processing functions

- C674x DSP @600MHz

- ✓ Minimum 1.2x enhancements in DSP Performance 19.2GMACs (16x16)

- CANFD\*1, CAN\*1

- ✓ Higher Bandwidth ECU Peripherals

- 3T4R RF

- ✓ Enhanced RF Performance (Gen 2)

- 300MHz ARM-R5F Lockstep MCU

- 3.5/4MB on-chip RAM

- HWA2.0 @300MHz

- C66x DSP @360MHz

- 100Mbps EMAC, 2x CAN-FD

- 3T4R/4T4R RF

#### 图 1. AWR2943/4 和 AWR1843 对比

可见 AWR2943/AWR2944 芯片不仅改进了射频性能(发射功率,噪声系数以及中频带宽等),在处理能力和内存容量上都有了显著提升,ARM-R5F 可以兼容 R4F 的代码,C66x DSP 核亦可以在 C674x DSP 核的代码基础上进一步提升算力,雷达加速器在提升频率的同时也加入了更多的算法支持。然而,对于开发者而言,如何将这些子系统有效的链接起来,充分利用总线带宽和内存容量,降低算法模块处理间的延时,是影响用户雷达系统性能的关键问题,本文将介绍 AWR2943/AWR2944 的内存和总线系统,同时将基于测试数据提供内存系统的优化建议,因为AWR2943 和 AWR2944 基于相同架构,仅在发射天线数量和内存容量上有所区别,本文将以 AWR2944 作为主要介绍。

### 2. AWR294x 内存系统

AWR2944 和 AWR2943 用户可使用的内存分别位于 DSS(C66x)和 MSS (ARM-R5F) 子系统内部,其中 DSS 内存为三级结构,MSS 为两级结构,其容量如下表,MSS 系统的 R5F 核仍可访问位于 DSS 上的 L1, L2 和 L3 内存,DSS 上的 C66x 核也可以对 MSS 的 L2 或 TCM 内存发起访问请求 (MSS\_L2 - 0xC0200000, MSS\_TCMB - 0xC1800000, MSS\_TCMA - 0xC1000000),具体的对应地址映射表在 AWR294x Technical Reference Manual 第 2 章 Memory Map。

| Device Variant   | DSS L3 | DSS L2 | DSS L1                 | MSS L2 | MSS L1                                                |

|------------------|--------|--------|------------------------|--------|-------------------------------------------------------|

| AWR2944 4MB      | 2.5MB  |        |                        |        | L1I:16KB                                              |

| AWR2943<br>3.5MB | 2MB    | 384KB  | L1P: 32KB<br>L1D: 32KB | 960KB  | L1D: 16KB<br>TCM 128KB<br>(TCMA: 64KB, TCMB:<br>64KB) |

表 1. AWR294x 内存系统容量

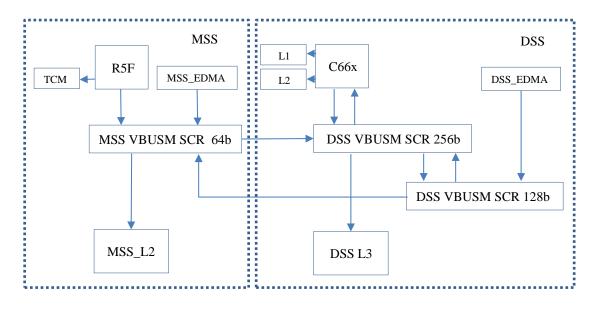

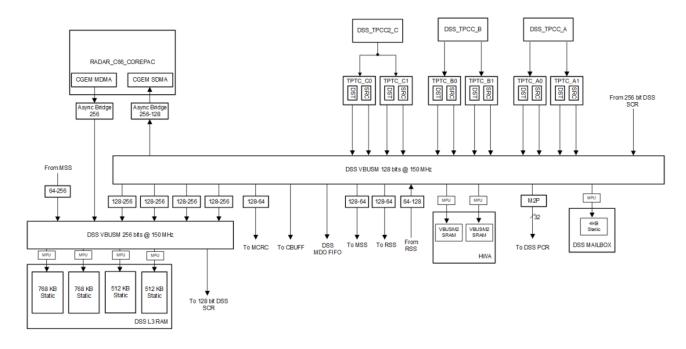

AWR294x 片上系统总线互联基于 TI 通用总线结构(Common Bus Architecture, CBA),主要由 VBUSM(Master 发起访问请求)与 VBUSP(Peripheral 接受访问请求)协议构成。AWR294x的总线运行频率为 150MHz,其中 MSS 的 VBUSM 总线为 64bit 带宽, 该总线上的各种设备,如 R5F,HSM,CPSW,EDMA TPCC等可以发起总线访问请求,通过 VBUSM 总线将访问请求送往对应外设,同时 VBUSM 也处理不同设备对于同一外设的访问请求并采取轮询(round robin)的方式进行优先级调度,MSS 系统的 L2 内存通过 VBUSM 总线进行访问; MSS 的 VBUSP 总线为 32bit 位宽,负责接受外部设备,如 DSS,RSS,R5F 以及来自 VBUSM 的访问请求。DSS 的 VBUSM 分成两部分,一部分带宽为 256bit,主要提供了对 DSS L3 内存的访问控制,256bit 的总线带宽可以有效的减少 DSS L3 内存的访问时延,C66x DSP 核以及来自 MSS 的访问请求可以直接通过该总线 访问 DSS L3,另一部分 DSS VBUSM 总线为 128bit 带宽,承担了连接 EDMA, HWA 等设备以及 C66x DSP 核对外设的访问请求, DSS VBUSP 总线则给 DSP 核与外设寄存器之间提供了交互通道。

由于本文将重点讨论如何进行用户软件的内存空间和效率优化,因此简化 R5F,C66x,EDMA 和各部分的内存连接的拓扑结构如下图,更加详细的总线结构图可以参考 AWR294x Technical Reference Manual 第 3 章 System Interconnect。

图 2. AWR294x 内存系统总线互联拓扑图

### 3. MSS 模块内存带宽测试及优化

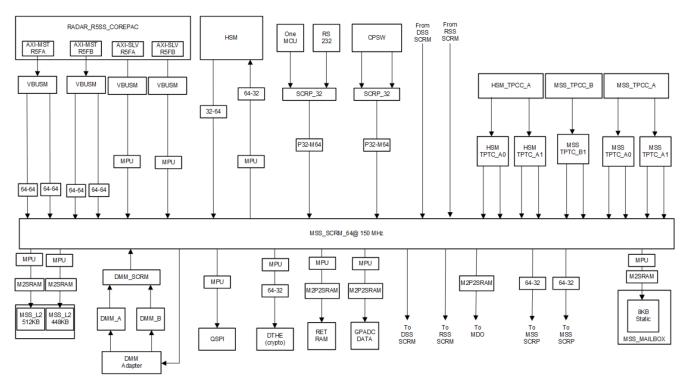

在 AWR294x 的 MSS 内部,集成了 ARM 公司的 Cortex-R5F 处理器,R5F 为 ARMv7-R 架构, AWR294x 的 R5F 处理器工作频率为 300MHz。

R5F 的 L1 内存系统主要包含 L1 Cache, TCM(Tightly-Coupled Memory)和内存保护单元(MPU); R5F L1 Cache 为哈弗结构,CPU 的指令通过 I-Cache 存取,数据通过 D-Cache 存取;TCM 与 L1 Cache 均属于 L1 内存系统,TCM 即可以存放指令,也可以用于数据读写,R5F 通过 ATCM 或 BTCM 端口对 TCM 内存进行访问,当 R5F 工作在 Lockstep 模式下时,其能访问的 TCMA 和 TCMB 的大小均为 64KB。 TCM 内存是 Non-cacheable Non-shared 的空间。

R5F 处理器通过 AMBA AXI 接口访问 VBUSM 总线上的 L2 内存,L2 内存可以配置为 Normal, Device 或者 Strongly Ordered 类型,需要注意的是 L1 Cache 可以缓存标记为 Cacheable 的 Normal 类型的 L2 地址,但是 对于 Device 和 Strongly Ordered 类型的 L2 地址是 Non-Cacheable 的,同时在访问这两种类型的 L2 地址时需要根据所采用的指令采用对齐访问,任何非对齐访问将会产生错误,详细的内容请参考 Cortex-R5 Technique Reference Manual 9.3.2 节 Strongly Ordered and Device transactions。

MSS 内部与 R5F 互联的总线结构如下图所示,HSM,CPSW 与 R5F 一样直接与 MSS 总线连接,因此这些模块访问 MSS L2 数据也有更好的效率。

图 3. MSS 内存总线系统

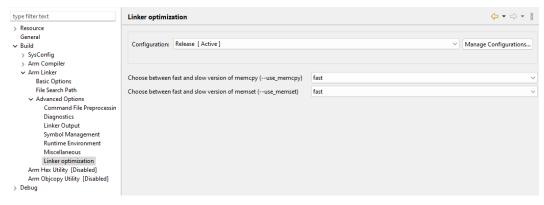

在 R5F 上运行标准库的 memcpy 函数进行不同内存空间的数据块拷贝,请注意在 ARM 的链接选项中需要将—use\_memcpy 和—use\_memset 选项都置于 fast 选项能够显著提升内存操作速度。

通常 L3 会配置为 Cached+Sharable 的模式。测试需要的时钟周期数和数据块大小(KB)的结果如下表,由结果可见,对于 R5F,由于 L3 位于 DSS 模块上,R5F 访问需要数个总线上的 Bridge,因此读取速率较低。

| Block Size  | 8192  | 4096  | 2048 | 1024 | 512  | 256 | 128 | 64  |

|-------------|-------|-------|------|------|------|-----|-----|-----|

| L2->L2      | 9886  | 4930  | 2492 | 1288 | 684  | 361 | 209 | 133 |

| L2->L3      | 9778  | 5273  | 2483 | 1275 | 667  | 355 | 217 | 120 |

| L3->L3      | 25644 | 12844 | 6444 | 3252 | 1652 | 844 | 450 | 237 |

| L3->L2      | 22575 | 11311 | 5679 | 2869 | 1461 | 751 | 406 | 217 |

| L2->TCMA(B) | 9800  | 4914  | 2483 | 1275 | 667  | 355 | 207 | 118 |

| TCMA(B)->L2 | 3633  | 1841  | 952  | 504  | 280  | 161 | 111 | 70  |

表 2. MSS R5F 数据访问速率

除了 R5F 可以访问内存以外,MSS 模块内部也集成了 EDMA 模块协助 R5F 进行数据块的传输,该 EDMA 模块有两个 TPCC(channel controller)控制器和三个 TPTC(transfer controller)控制器构成,TPCC 控制器可以通过用户配置响应系统事件或者软件发起的传输请求,并将这些请求发给 TPTC,TPTC 则负责数据搬移。EDMA搬移数据通过参数配置可以实现三维数据搬移,并支持 A-sync 或者 AB-sync 的触发方式,以此实现灵活的数据搬移以及重组。

在用户代码中通常需要将数据在 L2 以及 L3 之间进行传输,而 R5F 访问 L3 的效率很低,因此通常会使用 EDMA 进行 L2 和 L3 之间的数据拷贝,在 AWR2944 上测试 EDMA 进行拷贝测试所得结果如下,为避免中断时延, EDMA 的测试采用查询完成标志位的方式,所有结果均采用 R5F 时钟周期数进行对比。

| Block Size         | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64  |

|--------------------|------|------|------|------|-----|-----|-----|-----|

| L3 -> L3           | 2530 | 1424 | 877  | 635  | 496 | 406 | 382 | 368 |

| L3 -> TCM          | 2508 | 1458 | 947  | 629  | 520 | 406 | 382 | 368 |

| L3 -> L2           | 2508 | 1494 | 904  | 606  | 519 | 369 | 369 | 355 |

| TCM -> L3          | 2482 | 1445 | 877  | 635  | 520 | 382 | 406 | 392 |

| TCM -> L2          | 2490 | 1346 | 922  | 634  | 497 | 383 | 405 | 369 |

| L2 -> L2 same bank | 5048 | 2578 | 1448 | 894  | 497 | 383 | 405 | 391 |

| L2 -> L2 diff bank | 2530 | 1492 | 856  | 630  | 405 | 383 | 369 | 369 |

| L2 -> L3           | 2538 | 1433 | 897  | 629  | 520 | 382 | 382 | 368 |

表 3. MSS EDMA 数据访问速率

MSS 的 L2 分为两个 Bank,前 512KB(0x10200000~0x10280000)为 Bank 0,后 448KB(0x10280000~0x102F0000)为 Bank 1,不同的内存 Bank 可以同时响应读写指令,而同一 Bank 上的读写指令需要按顺序分时执行,因此在 EDMA 拷贝测试中,当数据块位于 L2 不同的 Bank 中,其拷贝速率高于源地址和目的地址数据位于同一 Bank 的情况。而对于 L3, L2 以及 TCM 之间的数据搬移,EDMA 的效率基本一致且远远高于使用 R5F 进行拷贝,因此在用户需要从 DSS L3 中搬移超过 128 Bytes 的数据到 MSS L2 中时都应视情况尽可能使用 EDMA 来提高代码执行效率。

### 4. DSS 模块内存带宽测试及优化

AWR294x DSS 子系统内部集成 C66x 系列 DSP 内核,通常毫米波数据处理链路将在 DSS 子系统上的 C66x 内核和 HWA 加速器进行处理,因此 DSS 内部的 L3 内存的访问采用了更大带宽(256 bits)的数据总线以达到快速访问数据的目的,如下图,DSS L3 分为 4 个 Bank,前两个 Bank 为 768KB, 后两个 Bank 为 512KB, 在同一时刻将数据访问均分到不同 Bank 上可以有效的帮助用户提高代码执行效率。

图 4. DSS 内存总线系统

同样在 DSS 模块上重复数据读写速率的测试,使用 DSP 核拷贝数据(采用标准库 memcpy 函数),通过在 Syscfg Cache 属性设置中将 L3 的 MAR 属性 Enable Cache 和 Prefetch,其速率如下表,但 DSP 不会自动维护 L3 上的 Cache 一致性,如果 L3 的内容与其它核(R5F 或 EDMA)共享访问,需程序员手动维护。

| Block Size | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 |

|------------|------|------|------|------|-----|-----|-----|----|

| L2 -> L2   | 4377 | 2189 | 1101 | 557  | 285 | 149 | 77  | 45 |

| L2 -> L3   | 6334 | 3109 | 1492 | 690  | 287 | 123 | 71  | 45 |

| L3 -> L2   | 4362 | 2217 | 1139 | 605  | 335 | 203 | 135 | 76 |

| L3 -> L3   | 8118 | 4047 | 2012 | 994  | 486 | 225 | 168 | 77 |

表 4. DSS DSP 数据访问速率

使用 EDMA 拷贝数据, 查询通道完成标志位模式

| Block Size         | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64  |

|--------------------|------|------|------|------|-----|-----|-----|-----|

| L2 -> L2           | 1803 | 1030 | 736  | 588  | 436 | 438 | 438 | 438 |

| L2 -> L3           | 1651 | 1033 | 734  | 586  | 436 | 436 | 436 | 436 |

| L3 -> L2           | 1647 | 1027 | 734  | 584  | 438 | 438 | 436 | 436 |

| L3 -> L3 same bank | 1941 | 1175 | 734  | 584  | 436 | 438 | 436 | 438 |

| L3 -> L3 diff bank | 1646 | 1032 | 736  | 586  | 436 | 436 | 436 | 436 |

表 5. DSS EDMA 数据访问速率

从上面结果可以看到启动 EDMA 到查询完成标志位的函数流程需要大约 430 左右的 DSP 时钟周期,对于 DSP L2 之间以及 L2 到 L3 的数据搬移,开启对 L3 Cache 属性之后,小于 1KB 的数据拷贝用 DSP 核可以更快完成,对于 L3 之间以及 L3 到 L2 的数据拷贝,则是小于 512B 使用 DSP 核更为快捷。

AWR294x 的 MCU 和 DSP 核上通常采用 Freertos 操作系统,在使用 EDMA 完成中断触发信号量的方式下,在 AWR294x DSP 上测得延时(从触发 EDMA 到获得信号量)约为 3000 时钟周期,用户应根据具体情况如 EDMA 和 DSP 数据流是否可以并行执行,是否有严格的数据延时需求等要求选取是否采用 EDMA 中断方式。

考虑到在用户使用过程中通常会有多个数据搬移的工作同时进行,亦测试了两个 EDMA 通道同时进行拷贝所需要的时间见表 6,测试 1 使用不同的 EDMA TC,源地址和目的地址都在同一个 Bank,测试 2 使用不同的 EDMA TC,但两组拷贝的数据源地址和目的地址都在不同的 Bank,测试 3 使用相同的 EDMA TC,源地址和目的地址位于不同的 Bank。测试中可以发现当采用不同的 TC,且源地址和目的地址都位于不同的 Bank 时可以充分利用 EDMA 和 L3 的访问带宽,因此在软件系统设计时较大数据块的内存位置应谨慎考虑,同时运行的 EDMA 通道应采用不同的 TC 减少排队等待。

| Block Size                   | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64  |

|------------------------------|------|------|------|------|-----|-----|-----|-----|

| L3 -> L3, diff TC, same bank | 3402 | 1901 | 1161 | 717  | 569 | 567 | 571 | 571 |

| L3 -> L3, diff TC, diff bank | 2070 | 1309 | 863  | 717  | 567 | 567 | 567 | 569 |

| L3 -> L3, same TC, diff bank | 3255 | 1752 | 1161 | 715  | 567 | 567 | 567 | 567 |

表 6. DSS EDMA 并发数据访问速率

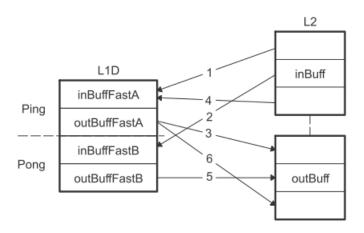

在 C66x 系统内部部署了另一套内部 DMA 系统称之为 IDMA,IDMA 可以在 C66x 核内部的 L1D,L1P,L2 内存之间进行数据拷贝(注意不能访问配置为 Cache 的地址段),并能提供最佳的拷贝速度,IDMA 有两个通道,其中通道 1 用于操作配置寄存器,可以很方便的对一些需要重复配置的寄存器进行修改,通道 2 用于在 L1 和 L2 的内存之间进行顺序拷贝,注意其与 EDMA 不同的是 IDMA 只能按地址方向线性增长的方向进行寻址,EDMA 的寻址方式更为灵活。AWR294x C66x 核的 IDMA 实测速度如下

| Block Size | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 |

|------------|------|------|------|------|-----|-----|-----|----|

| L2 -> L2   | 2578 | 1278 | 654  | 316  | 160 | 82  | 56  | 56 |

| L2 -> L1   | 1068 | 561  | 295  | 162  | 108 | 82  | 56  | 56 |

| L1 -> L2   | 1071 | 564  | 298  | 164  | 111 | 84  | 57  | 57 |

表 7. DSS IDMA 数据访问速率

IDMA 提供了一种高效的从 L1, L2 的数据拷贝通路,它只需要配置 4 个寄存器(IDMA1\_SOURCE,IDMA1\_DEST,IDMA1\_COUNT,IDMA1\_STAT),用户易于操作,在雷达的处理链路中,用户经常需要将大量的数据拆分成小段(距离、速度维度向量)进行处理,所以需要在 L1D 内存中开启 ping-pong 缓存以提高算法的执行效率,IDMA 不仅可以降低数据拷贝的延时,同时也可以与 DSP 核并行操作(如下图),对算法的执行速度提高很大。

图 5. IDMA 使用方法示例

### 5. 总结

在基于 AWR294x 开发的毫米波雷达的产品中,因为数据量访问的量比较大,内存读写的的效率直接关系到是否能够在需求时间内完成数据的处理,本文对 AWR294x 片上 MSS 以及 DSS 的内存系统进行读写带宽测试,基于这些结果,介绍了如何在 AWR294x 工程中对内存读写效率进行优化,同时 AM273x 系列 MCU 处理器亦可作为参考。

### 参考文献

- 1. swrs273a, AWR2943/44 Single-Chip 76- and 81-GHz FMCW Radar Sensor datasheet (Rev. A)

- 2. spruiv5, AWR294x Technical Reference Manual (Rev. C)

- 3. sprugw0, <u>C66x CorePac User's Guide (Rev. C)</u>

- 4. sprugy8, C66x DSP Cache User's Guide

- 5. sprabg7, Optimizing Loops on the C66x DSP

- 6. Cortex-R5 Technical Reference Manual <a href="https://developer.arm.com/documentation/ddi0460/latest/">https://developer.arm.com/documentation/ddi0460/latest/</a>

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司