# 5V 接口

# 说明

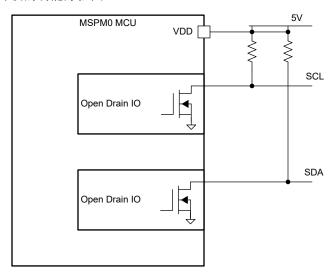

该示例演示了如何使用 MSPM0 器件上的漏极开路 IO (ODIO)与高达 5V 的信号进行连接。通过使用外部上拉电阻器,开漏 IO 允许在高于 MSPM0 V<sub>DD</sub> 电源电压的电压电平下跨多个电压域进行通信。

图 1 显示了该示例中使用的外设的功能方框图。

图 1. 子系统功能方框图

## 所需外设

该应用最多可以使用两个开漏 IO。

#### 表 1.

| 子块功能 | 外设使用       | 说明                        |

|------|------------|---------------------------|

| IO   | 2个 GPIO 引脚 | PAO 和 PA1,只能使用 5V 容限开漏 IO |

## 兼容器件

根据表 1 中的要求,该示例与表 2 中的器件兼容。相应的 EVM 可用于原型设计。

#### 表 2.

| 兼容器件      | EVM           |

|-----------|---------------|

| MSPM0Lxxx | LP-MSPM0L1306 |

| MSPM0Gxxx | LP-MSPM0G3507 |

## 设计步骤

- 1. 连接相应的跳线。

- 2. 确定应用所需的上拉电阻。

- a. 所需的上拉强度取决于应用的时序要求和连接的电容。要获得更大的电容,您需要具有更强(即低电阻)的上拉。关于确定确切的上拉电阻的讨论超出了本文档的范围,但可以在 I2C 总线上拉电阻器计算应用手册中找到。

- 3. 在 SysConfig 中通过软件配置在这些引脚上使用的外设(例如 UART、I2C 或计时器)。

- 4. 根据使用的外设编写应用程序代码。

#### 设计注意事项

- 1. 上拉电阻器:需要使用一个上拉电阻器为 ODIO 上的 I2C 和 UART 功能输出高电平。

- 2. 驱动强度控制:这不适用于 ODIO 类型。

## 附加资源

- 下载 MSPM0 SDK

- 了解有关 SysConfig 的更多信息

- MSPM0L LaunchPad

- MSPM0G LaunchPad

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司