Public Version

# CC2538 System-on-Chip Solution for 2.4-GHz IEEE 802.15.4 and ZigBee®/ZigBee IP® Applications

Texas Instruments CC2538<sup>™</sup> Family of Products Version C

# **User's Guide**

Literature Number: SWRU319C April 2012–Revised May 2013

# **WARNING: EXPORT NOTICE**

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorisation from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

US ECCN: 5E002 EU ECCN: 5E002

And may require export or re-export license for shipping it in compliance with the applicable regulations of certain countries.

# Public Version

# **Contents**

| Prefa | се    |          |                                              | 26 |

|-------|-------|----------|----------------------------------------------|----|

| 1     | Archi | itectura | ıl Overview                                  | 32 |

|       | 1.1   |          | Applications                                 |    |

|       | 1.2   | •        | ew                                           |    |

|       | 1.3   |          | onal Overview                                |    |

|       |       | 1.3.1    | ARM Cortex-M3                                | 36 |

|       |       | 1.3.1    | .1 Processor Core                            | 36 |

|       |       | 1.3.1    | .2 Memory Map                                | 36 |

|       |       | 1.3.1    |                                              |    |

|       |       | 1.3.1    |                                              |    |

|       |       | 1.3.1    | ·                                            |    |

|       |       | 1.3.1    | .6 MPU                                       | 37 |

|       |       | 1.3.2    | On-Chip Memory                               | 37 |

|       |       | 1.3.2    | 2.1 SRAM                                     | 37 |

|       |       | 1.3.2    | 2.2 Flash Memory                             | 37 |

|       |       | 1.3.2    | 2.3 ROM                                      | 38 |

|       |       | 1.3.3    | Radio                                        | 38 |

|       |       | 1.3.4    | AES Engine with 128, 192 256 Bit Key Support | 38 |

|       |       | 1.3.5    | Programmable Timers                          | 38 |

|       |       | 1.3.5    | 5.1 MAC Timer                                | 39 |

|       |       | 1.3.5    | 5.2 Watchdog Timer                           | 39 |

|       |       | 1.3.5    | S.3 Sleep Timer                              | 39 |

|       |       | 1.3.5    | 5.4 CCP Pins                                 | 39 |

|       |       | 1.3.6    | Direct Memory Access                         | 39 |

|       |       | 1.3.7    | System Control and Clock                     | 40 |

|       |       | 1.3.8    | Serial Communications Peripherals            | 41 |

|       |       | 1.3.8    | 3.1 USB                                      | 41 |

|       |       | 1.3.8    | 3.2 UART                                     | 41 |

|       |       | 1.3.8    | 3.3 I <sup>2</sup> C                         | 42 |

|       |       | 1.3.8    | 3.4 SSI                                      | 43 |

|       |       | 1.3.9    | Programmable GPIOs                           | 43 |

|       |       | 1.3.10   | Analog                                       | 43 |

|       |       | 1.3.1    | 0.1 ADC                                      | 44 |

|       |       | 1.3.1    | 0.2 Analog Comparator                        | 44 |

|       |       | 1.3.1    | 0.3 Random Number Generator                  | 44 |

|       |       | 1.3.11   | cJTAG, JTAG and SWO                          | 44 |

|       |       | 1.3.12   | Packaging and Temperature                    | 44 |

| 2     | The C | Cortex-  | M3 Processor                                 | 45 |

|       | 2.1   | The Co   | ortex-M3 Processor Introduction              | 46 |

|       | 2.2   |          | Diagram                                      |    |

|       | 2.3   |          | ew                                           |    |

|       |       | 2.3.1    | System-Level Interface                       |    |

|       |       | 2.3.2    | Integrated Configurable Debug                |    |

|       |       | 2.3.3    | Trace Port Interface Unit                    |    |

|   |       | 2.3.4 Cortex-M3 System Component Details                         | 48         |

|---|-------|------------------------------------------------------------------|------------|

|   | 2.4   | Programming Model                                                | 48         |

|   |       | 2.4.1 Processor Mode and Privilege Levels for Software Execution | 49         |

|   |       | 2.4.2 Stacks                                                     | 49         |

|   |       | 2.4.3 Register Map                                               | 49         |

|   |       | 2.4.4 Register Descriptions                                      | 51         |

|   |       | 2.4.5 Exceptions and Interrupts                                  | 61         |

|   |       | 2.4.6 Data Types                                                 | 61         |

|   | 2.5   | Instruction Set Summary                                          | 61         |

| 3 | Corte | ex™-M3 Peripherals                                               | 65         |

|   | 3.1   | Cortex™-M3 Peripherals Introduction                              | 66         |

|   | 3.2   | Functional Description                                           | 66         |

|   |       | 3.2.1 SysTick                                                    | 66         |

|   |       | 3.2.2 NVIC                                                       | 67         |

|   |       | 3.2.2.1 Level-Sensitive and Pulse Interrupts                     | 67         |

|   |       | 3.2.2.2 Hardware and Software Control of Interrupts              | 67         |

|   |       | 3.2.3 SCB                                                        |            |

|   |       | 3.2.4 MPU                                                        | 68         |

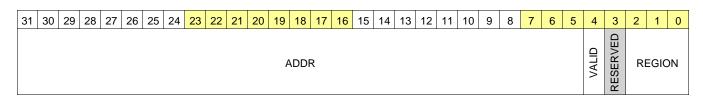

|   |       | 3.2.4.1 Updating an MPU Region                                   | 69         |

|   |       | 3.2.4.1.1 Updating an MPU Region Using Separate Words            |            |

|   |       | 3.2.4.1.2 Updating an MPU Region Using Multiple-Word Writes      |            |

|   |       | 3.2.4.1.3 Subregions                                             |            |

|   |       | 3.2.4.2 MPU Access Permission Attributes                         |            |

|   |       | 3.2.4.2.1 MPU Configuration for a CC2538 Microcontroller         | 72         |

|   |       | 3.2.4.3 MPU Mismatch                                             |            |

|   | 3.3   | Register Map                                                     |            |

|   | 3.4   | SysTick Register Descriptions                                    |            |

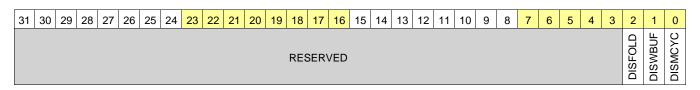

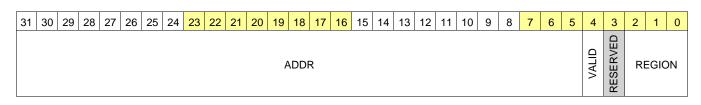

|   | 3.5   | NVIC Register Descriptions                                       |            |

|   |       | 3.5.1 System Control Block (SCB) Register Descriptions           |            |

|   |       | 3.5.2 MPU Register Descriptions                                  |            |

| 4 | Mem   | ory Map 1                                                        | 155        |

| • | 4.1   | Memory Model                                                     |            |

|   | 7.1   | 4.1.1 Memory Regions, Types, and Attributes                      |            |

|   |       | 4.1.2 Memory System Ordering of Memory Accesses                  |            |

|   |       | 4.1.3 Behavior of Memory Accesses                                |            |

|   |       | ·                                                                | 158<br>158 |

|   |       |                                                                  | 159        |

|   |       | · · · · · · · · · · · · · · · · · · ·                            | 161        |

|   |       | 4.1.5.2 Directly Accessing a Bit-Band Region                     |            |

|   |       |                                                                  | 161        |

|   |       |                                                                  | 162        |

| _ |       | •                                                                |            |

| 5 |       | •                                                                | 164        |

|   | 5.1   | ·                                                                | 165        |

|   |       |                                                                  | 165        |

|   |       | 1 21                                                             | 165        |

|   |       | ·                                                                | 170        |

|   |       |                                                                  | 170        |

|   |       | !                                                                | 171        |

|   |       | 1 , 1 9                                                          | 172        |

|   |       | · · · · ·                                                        | 172        |

|   |       | , ,                                                              | 172        |

|   |       | 5.1.7.2 Exception Return                                         | 173        |

|   |       |                                                                  |            |

|   | 5.2        | Fault Handling                                                 | 174 |

|---|------------|----------------------------------------------------------------|-----|

|   |            | 5.2.1 Fault Types                                              | 174 |

|   |            | 5.2.2 Fault Escalation and Hard Faults                         | 175 |

|   |            | 5.2.3 Fault Status Registers and Fault Address Registers       | 175 |

|   |            | 5.2.4 Lockup                                                   | 176 |

|   |            | 5.2.5 PKA Interrupt                                            | 176 |

| 6 | ΙΤΔΟ       | S Interface                                                    | 177 |

| • | 6.1        | Debug Port                                                     |     |

|   | 6.2        | IEEE 1149.7                                                    |     |

|   | 6.3        | Switching Debug Interface from 2-pin cJTAG to 4-pin JTAG       |     |

|   | 6.4        | Debugger Connection                                            |     |

|   | 0.4        |                                                                |     |

|   |            | 6.4.1.1 Default Boot Mode                                      |     |

|   |            |                                                                |     |

|   | 0.5        | 6.4.1.2 CM3 DAP Access                                         |     |

|   | 6.5        | Primary Debug Support                                          |     |

|   |            | 6.5.1 Processor Native Debug Support                           |     |

|   |            | 6.5.1.1 Cortex™-M3 MPU                                         |     |

|   |            | 6.5.2 Suspend                                                  |     |

|   | 6.6        | Debug Access Security Through ICEPick                          |     |

|   |            | 6.6.1 Unlocking the Debug Interface                            |     |

|   | 6.7        | CM3 Debug Interrupt                                            | 183 |

| 7 | Syste      | em Control                                                     | 184 |

|   | 7.1        | Power Management                                               | 185 |

|   |            | 7.1.1 Control Inputs to Power Management                       | 185 |

|   |            | 7.1.1.1 Clock Gating Registers                                 | 185 |

|   |            | 7.1.1.2 Deep Sleep Selector (SYSCTRL Register)                 |     |

|   |            | 7.1.1.3 Power Mode Configuration Register (PMCTL Register)     |     |

|   |            | 7.1.1.4 WFI - Operational Mode Initiator (Wait For Interrupt)  |     |

|   |            | 7.1.2 Using Power Management                                   |     |

|   |            | 7.1.2.1 Sequencing when using Power Modes                      |     |

|   |            | 7.1.2.2 Time Considerations for Active, Sleep and PM0          |     |

|   |            | 7.1.2.3 Time Considerations for PM1, PM2 and PM3               |     |

|   |            | 7.1.2.3.1 Enter Power Mode when Running on 16 MHz System Clock |     |

|   |            | 7.1.2.3.2 Enter Power Mode when Running on 32 MHz System Clock |     |

|   |            | 7.1.2.4 Exit from Power Modes                                  |     |

|   |            | 7.1.2.4.1 32 MHz XOSC Startup Time                             |     |

|   |            | 7.1.2.4.2 32 MHz Qualification Time                            |     |

|   |            | 7.1.3 Power Consumption                                        |     |

|   | 7.2        | Oscillators and Clocks                                         |     |

|   | 1.2        | 7.2.1 High Frequency Oscillators                               |     |

|   |            | 7.2.1.1 16 MHz RCOSC Calibration                               |     |

|   |            | 7.2.2 Low Frequency Oscillators                                | 194 |

|   |            | 7.2.2.1 32 kHz RCOSC Calibration                               | 194 |

|   | 7.3        | System Clock Gating                                            | 194 |

|   | 7.3        | 7.3.1 Clocks for UART and SSI                                  | 194 |

|   |            |                                                                |     |

|   | 7.4        |                                                                | 195 |

|   | 7.4        | Reset                                                          | 195 |

|   |            | 7.4.1 Reset of Peripherals                                     | 196 |

|   |            | 7.4.2 Power-On Reset and Brownout Detector                     |     |

|   | <b>-</b> - | 7.4.3 Clock Loss Detector                                      |     |

|   | 7.5        | Emulator in Power Modes                                        |     |

|   | 7.6        | Chip State Retention                                           |     |

|   |            | 7.6.1 CRC Check on State Retention                             | 197 |

|   | 7.7    | System Control Registers                                      | 197 |

|---|--------|---------------------------------------------------------------|-----|

|   |        | 7.7.1 SYS_CTRL Registers                                      | 197 |

|   |        | 7.7.1.1 SYS_CTRL Registers Mapping Summary                    | 197 |

|   |        | 7.7.1.2 SYS_CTRL Register Descriptions                        | 199 |

| 8 | Interi | nal Memory                                                    | 214 |

|   | 8.1    | Introduction                                                  |     |

|   | 8.2    | Flash Memory Organization                                     | 215 |

|   |        | 8.2.1 Information Page                                        | 215 |

|   |        | 8.2.2 Lock Bit Page                                           | 215 |

|   | 8.3    | Flash Write                                                   | 215 |

|   |        | 8.3.1 Flash Write Procedure                                   | 215 |

|   |        | 8.3.2 Writing Multiple Times to a Word                        | 216 |

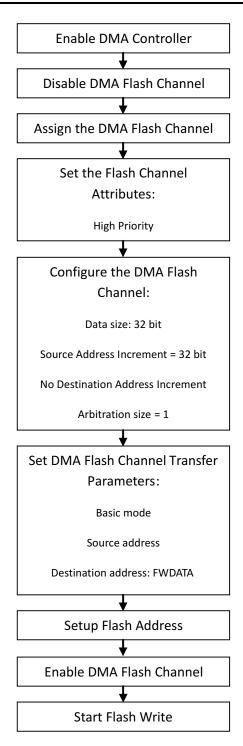

|   |        | 8.3.3 DMA Flash Write                                         | 217 |

|   |        | 8.3.4 CPU Flash Write                                         | 218 |

|   | 8.4    | Flash DMA Trigger                                             | 219 |

|   | 8.5    | Flash Page Erase                                              | 219 |

|   |        | 8.5.1 Performing Flash Erase from Flash Memory                | 219 |

|   | 8.6    | Flash Lock Bit Page and Customer Configuration Area (CCA)     | 219 |

|   |        | 8.6.1 Flash Image Valid Bits in Lock Bit Page                 | 221 |

|   |        | 8.6.2 ROM Boot Loader Backdoor Configuration in Lock Bit Page | 221 |

|   | 8.7    | Flash Mass Erase                                              | 222 |

|   |        | 8.7.1 Flash Mass Erase Procedure                              | 223 |

|   | 8.8    | ROM Sub System                                                | 224 |

|   | 8.9    | SRAM                                                          | 224 |

|   | 8.10   | Flash Control Registers                                       | 225 |

|   |        | 8.10.1 FLASH_CTRL Registers                                   | 225 |

|   |        | 8.10.1.1 FLASH_CTRL Registers Mapping Summary                 | 225 |

|   |        | 8.10.1.2 FLASH_CTRL Register Descriptions                     | 225 |

| 9 | Gene   | eral-Purpose Inputs/Outputs                                   | 230 |

|   | 9.1    | I/O Control                                                   | 231 |

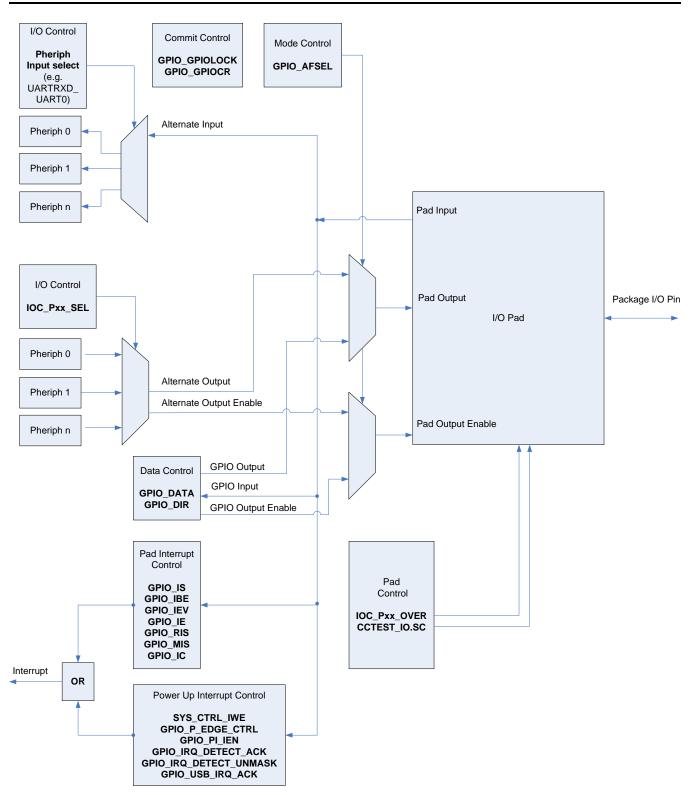

|   |        | 9.1.1 I/O Muxing                                              | 231 |

|   | 9.2    | GPIO                                                          | 232 |

|   |        | 9.2.1 General-Purpose Inputs/Outputs                          | 232 |

|   |        | 9.2.2 Functional Description                                  | 232 |

|   |        | 9.2.2.1 Data Control                                          | 234 |

|   |        | 9.2.2.1.1 Data Direction Operation                            | 234 |

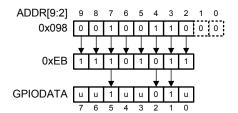

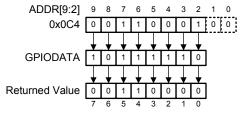

|   |        | 9.2.2.1.2 Data Register Operation                             | 234 |

|   |        | 9.2.2.2 Interrupt Control                                     | 234 |

|   |        | 9.2.2.2.1 Power-Up Interrupt                                  | 235 |

|   |        | 9.2.2.3 Mode Control                                          | 235 |

|   |        | 9.2.2.4 Commit Control                                        | 235 |

|   |        | 9.2.2.5 Pad Control                                           | 236 |

|   |        | 9.2.3 Configuration                                           | 237 |

|   |        | 9.2.4 Radio Test Output Signals                               | 238 |

|   |        | 9.2.5 Power-Down Signal MUX (PMUX)                            | 238 |

|   | 9.3    | I/O Control and GPIO Registers                                | 238 |

|   |        | 9.3.1 GPIO Registers                                          | 238 |

|   |        | 9.3.1.1 GPIO Registers Mapping Summary                        | 238 |

|   |        | 9.3.1.1.1 GPIO Common Registers Mapping                       |     |

|   |        | 9.3.1.1.2 GPIO Instances Register Mapping Summary             |     |

|   |        | 9.3.1.2 GPIO Common Register Descriptions                     |     |

|   |        | 9.3.2 IOC Registers                                           |     |

|   |        | 9.3.2.1 IOC Registers Mapping Summary                         |     |

|   |        |                                                               |     |

|    |       | 9.3.2.2 IOC Register Descriptions                     | 257 |

|----|-------|-------------------------------------------------------|-----|

| 10 | Micro | o Direct Memory Access 2                              | 85  |

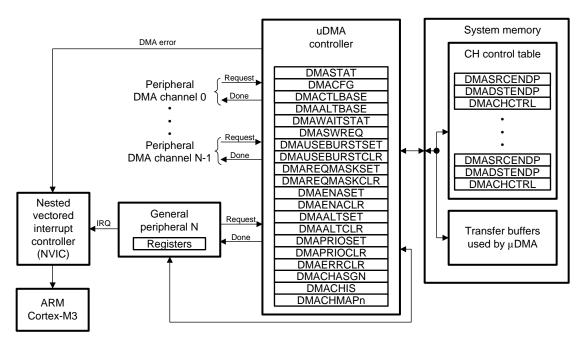

|    | 10.1  | μDMA Introduction                                     |     |

|    | 10.2  | Block Diagram                                         | 286 |

|    | 10.3  | Functional Description                                | 287 |

|    |       | 10.3.1 Channel Assignments                            | 287 |

|    |       | 10.3.2 Priority                                       | 289 |

|    |       | 10.3.3 Arbitration Size                               | 289 |

|    |       | 10.3.4 Request Types                                  | 289 |

|    |       | 10.3.4.1 Single Request                               | 290 |

|    |       | 10.3.4.2 Burst Request                                | 290 |

|    |       | · · · · · · · · · · · · · · · · · · ·                 | 290 |

|    |       | 10.3.6 Transfer Modes                                 | 291 |

|    |       | ·                                                     | 291 |

|    |       | 10.3.6.2 Basic Mode                                   |     |

|    |       | 10.3.6.3 Auto Mode                                    |     |

|    |       | 10.3.6.4 Ping-Pong                                    |     |

|    |       | 10.3.6.5 Memory Scatter-Gather                        |     |

|    |       | 10.3.6.6 Peripheral Scatter-Gather                    |     |

|    |       | 10.3.7 Transfer Size and Increment                    |     |

|    |       | ·                                                     | 300 |

|    |       | •                                                     | 300 |

|    | 40.4  | ·                                                     | 301 |

|    | 10.4  |                                                       | 301 |

|    |       |                                                       | 301 |

|    |       | 10.4.2 Configuring a Memory-to-Memory Transfer        |     |

|    |       | 10.4.2.1 Configure the Channel Attributes             |     |

|    |       | 10.4.2.2 Configure the Channel Control Structure      |     |

|    |       | 10.4.2.3 Start the Transfer                           |     |

|    |       | 10.4.3 Configuring a Peripheral for Simple Transmit   |     |

|    |       | 10.4.3.1 Configure the Channel Attributes             |     |

|    |       | 10.4.3.2 Configure the Channel Control Structure      |     |

|    |       | 10.4.3.2.1 Configure the Source and Destination       |     |

|    |       | 10.4.3.3 Start the Transfer                           |     |

|    |       | 10.4.4 Configuring a Peripheral for Ping-Pong Receive |     |

|    |       | 10.4.4.1 Configure the Channel Attributes             |     |

|    |       | 10.4.4.2 Configure the Channel Control Structure      |     |

|    |       | 10.4.4.2.1 Configure the Source and Destination       |     |

|    |       | -                                                     | 305 |

|    |       |                                                       | 306 |

|    |       | 10.4.4.5 Process Interrupts                           | 306 |

|    |       | 10.4.5 Configuring Channel Assignments                | 306 |

|    | 10.5  | μDMA Registers                                        | 306 |

|    |       | 10.5.1 UDMA Registers                                 | 306 |

|    |       | 10.5.1.1 UDMA Registers Mapping Summary               | 306 |

|    |       | 10.5.1.2 UDMA Register Descriptions                   | 307 |

| 11 | Gene  | eral-Purpose Timers                                   | 18  |

|    | 11.1  | •                                                     | 319 |

|    | 11.2  | ·                                                     | 319 |

|    | 11.3  | Functional Description                                | 320 |

|    |       |                                                       | 320 |

|    |       | 11.3.2 Timer Modes                                    | 321 |

|    |       |                                                       |     |

|     |             | 11.3.2.1 One-Shot or Periodic Timer Mode                          | 224 |

|-----|-------------|-------------------------------------------------------------------|-----|

|     |             |                                                                   |     |

|     |             | 11.3.2.2 Input Edge-Count Mode                                    |     |

|     |             | 11.3.2.3 Input Edge-Time Mode                                     |     |

|     |             | 11.3.2.4 PWM Mode                                                 |     |

|     |             | 11.3.3 Wait-for-Trigger Mode                                      |     |

|     |             | 11.3.4 Synchronizing GP Timer Blocks                              |     |

|     |             | 11.3.5 Accessing Concatenated 16- and 32-Bit GPTM Register Values |     |

|     | 11.4        | Initialization and Configuration                                  |     |

|     |             | 11.4.1 One-Shot and Periodic Timer Modes                          |     |

|     |             | 11.4.2 Input Edge-Count Mode                                      |     |

|     |             | 11.4.3 Input Edge-Timing Mode                                     |     |

|     |             | 11.4.4 PWM Mode                                                   |     |

|     | 11.5        | General-Purpose Timer Registers                                   |     |

|     |             | 11.5.1 GPTIMER Registers                                          |     |

|     |             | 11.5.1.1 GPTIMER Registers Mapping Summary                        |     |

|     |             | 11.5.1.1.1 GPTIMER Common Registers Mapping                       |     |

|     |             | 11.5.1.1.2 GPTIMER Instances Register Mapping Summary             | 331 |

|     |             | 11.5.1.2 GPTIMER Common Register Descriptions                     | 335 |

| 12  | MAC         | Timer                                                             | 350 |

|     | 12.1        | Timer Operation                                                   |     |

|     |             | 12.1.1 General                                                    |     |

|     |             | 12.1.2 Up Counter                                                 |     |

|     |             | 12.1.3 Timer Overflow                                             |     |

|     |             | 12.1.4 Timer Overnow                                              |     |

|     |             | 12.1.5 Timer Compare                                              |     |

|     |             | 12.1.6 Overflow Count                                             |     |

|     |             | 12.1.7 Overflow-Count Update                                      |     |

|     |             | ·                                                                 |     |

|     |             |                                                                   |     |

|     |             | 12.1.9 Overflow-Count Compare                                     |     |

|     | 40.0        | 12.1.10 Capture Input                                             | 352 |

|     | 12.2        | Interrupts                                                        |     |

|     | 12.3        | Event Outputs (DMA Trigger and Radio Events)                      |     |

|     | 12.4        | Timer Start and Stop Synchronization                              |     |

|     |             | 12.4.1 General                                                    |     |

|     |             | 12.4.2 Timer Synchronous Stop                                     |     |

|     |             | 12.4.3 Timer Synchronous Start                                    | 354 |

|     | 12.5        | MAC Timer Registers                                               |     |

|     |             | 12.5.1 RFCORE_SFR Registers                                       |     |

|     |             | 12.5.1.1 RFCORE_SFR Registers Mapping Summary                     |     |

|     |             | 12.5.1.2 RFCORE_SFR Register Descriptions                         | 356 |

| 13  | Sleep       | Timer                                                             | 362 |

|     | 13.1        | General                                                           | 363 |

|     | 13.2        | Timer Compare                                                     | 363 |

|     | 13.3        | Timer Capture                                                     | 363 |

|     | 13.4        | Sleep Timer Registers                                             | 364 |

|     |             | 13.4.1 SMWDTHROSC Registers                                       |     |

|     |             | 13.4.1.1 SMWDTHROSC Registers Mapping Summary                     |     |

|     |             | 13.4.1.2 SMWDTHROSC Register Descriptions                         |     |

| 1.4 | \ <i>\\</i> |                                                                   |     |

| 14  |             | hdog Timer                                                        |     |

|     | 14.1        | Watchdog Timer                                                    | 371 |

|     | 14.2        | Watchdog Timer Registers                                          |     |

|     |             | 14.2.1 SMWDTHROSC Registers                                       |     |

|     |             | 14.2.1.1 SMWDTHROSC Registers Mapping Summary                     | 371 |

|     |       | 14.2.1.2 SMWDTHROSC Register Descriptions         | 371 |

|-----|-------|---------------------------------------------------|-----|

| 15  | ADC   |                                                   | 373 |

|     | 15.1  | ADC Introduction                                  | 374 |

|     | 15.2  | ADC Operation                                     | 374 |

|     |       | 15.2.1 ADC Inputs                                 | 374 |

|     |       | 15.2.2 ADC Conversion Sequences                   | 375 |

|     |       | 15.2.3 Single ADC Conversion                      | 375 |

|     |       | 15.2.4 ADC Operating Modes                        | 375 |

|     |       | 15.2.5 ADC Conversion Results                     |     |

|     |       | 15.2.6 ADC Reference Voltage                      |     |

|     |       | 15.2.7 ADC Conversion Timing                      |     |

|     |       | 15.2.8 ADC Interrupts                             | 376 |

|     |       | 15.2.9 ADC DMA Triggers                           | 376 |

|     | 15.3  | Analog-to-Digital Converter Registers             | 377 |

|     |       | 15.3.1 SOC_ADC Registers                          | 377 |

|     |       | 15.3.1.1 SOC_ADC Registers Mapping Summary        | 377 |

|     |       | 15.3.1.2 SOC_ADC Register Descriptions            | 377 |

| 16  | Rand  | lom Number Generator                              | 381 |

| . • | 16.1  | Introduction                                      |     |

|     | 16.2  | Random-Number-Generator Operation                 |     |

|     |       | 16.2.1 Pseudo-random Sequence Generation          |     |

|     |       | 16.2.2 Seeding                                    |     |

|     |       | 16.2.3 CRC16                                      |     |

|     | 16.3  | Random Number Generator Registers                 |     |

|     |       | 16.3.1 SOC_ADC Registers                          |     |

|     |       | 16.3.1.1 SOC_ADC Registers Mapping Summary        |     |

|     |       | 16.3.1.2 SOC_ADC Register Descriptions            |     |

| 17  | Analo | og Comparator                                     | 385 |

|     | 17.1  | Introduction                                      |     |

|     | 17.2  | Analog Comparator Registers                       |     |

|     |       | 17.2.1 SOC_ADC Registers                          |     |

|     |       | 17.2.1.1 SOC_ADC Registers Mapping Summary        |     |

|     |       | 17.2.1.2 SOC_ADC Register Descriptions            |     |

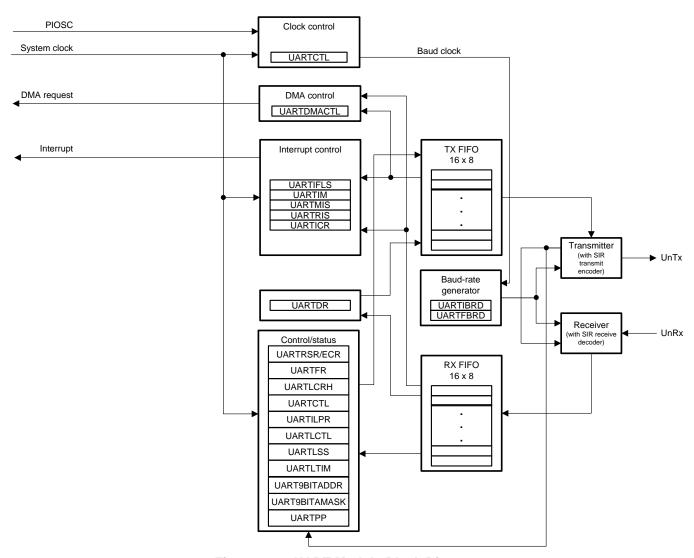

| 18  | Unive | ersal Asynchronous Receivers and Transmitters     |     |

| 10  | 18.1  | Universal Asynchronous Receivers and Transmitters |     |

|     | 18.2  | Block Diagram                                     |     |

|     | 18.3  | Signal Description                                |     |

|     | 18.4  | Functional Description                            |     |

|     | 10.4  | 18.4.1 Transmit and Receive Logic                 |     |

|     |       | 18.4.2 Baud-Rate Generation                       |     |

|     |       | 18.4.3 Data Transmission                          |     |

|     |       | 18.4.4 Modem Handshake Support                    |     |

|     |       | 18.4.4.1 Signaling                                | 392 |

|     |       | 18.4.4.2 Flow Control                             | 392 |

|     |       | 18.4.4.2.1 Hardware Flow Control (RTS and CTS)    |     |

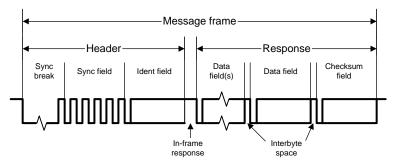

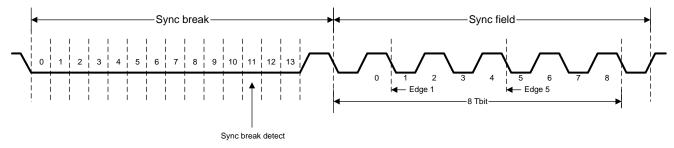

|     |       | 18.4.5 LIN Support                                |     |

|     |       | 18.4.5.1 LIN Master                               |     |

|     |       | 18.4.5.2 LIN Slave                                | 393 |

|     |       | 18.4.6 9-Bit UART Mode                            | 394 |

|     |       | 18.4.7 FIFO Operation                             | 394 |

|     |       | 18.4.8 Interrupts                                 | 395 |

|     |       | 18.4.9 Loopback Operation                         |     |

|     |       | 1 1                                               |     |

|    | 18.5 | Initialization and Configuration                             |     |

|----|------|--------------------------------------------------------------|-----|

|    | 18.6 | UART Registers                                               | 396 |

|    |      | 18.6.1 UART Registers                                        | 396 |

|    |      | 18.6.1.1 UART Registers Mapping Summary                      | 396 |

|    |      | 18.6.1.1.1 UART Common Registers Mapping                     |     |

|    |      | 18.6.1.1.2 UART Instances Register Mapping Summary           | 397 |

|    |      | 18.6.1.2 UART Common Register Descriptions                   | 398 |

| 19 | Sync | hronous Serial Interface                                     | 415 |

|    | 19.1 | Synchronous Serial Interface                                 |     |

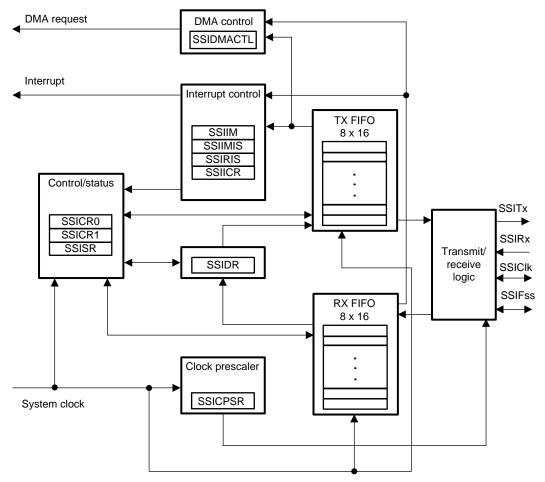

|    | 19.2 | Block Diagram                                                | 416 |

|    | 19.3 | Signal Description                                           | 417 |

|    | 19.4 | Functional Description                                       |     |

|    |      | 19.4.1 Bit Rate Generation                                   |     |

|    |      | 19.4.2 FIFO Operation                                        |     |

|    |      | 19.4.2.1 Transmit FIFO                                       |     |

|    |      | 19.4.2.2 Receive FIFO                                        |     |

|    |      | 19.4.3 Interrupts                                            |     |

|    |      | 19.4.4 Frame Formats                                         |     |

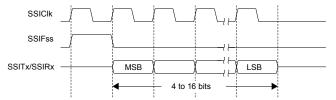

|    |      | 19.4.4.1 Texas Instruments Synchronous Serial Frame Format   |     |

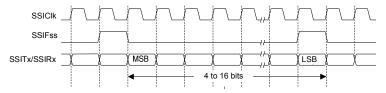

|    |      | 19.4.4.2 Freescale SPI Frame Format                          |     |

|    |      | 19.4.4.2.1 SPO Clock Polarity Bit                            |     |

|    |      | 19.4.4.2.2 SPH Phase Control Bit                             |     |

|    |      | 19.4.4.3 Freescale SPI Frame Format With SPO = 0 and SPH = 0 |     |

|    |      | 19.4.4.4 Freescale SPI Frame Format With SPO = 0 and SPH = 1 |     |

|    |      | 19.4.4.5 Freescale SPI Frame Format With SPO = 1 and SPH = 0 |     |

|    |      | 19.4.4.6 Freescale SPI Frame Format With SPO = 1 and SPH = 1 |     |

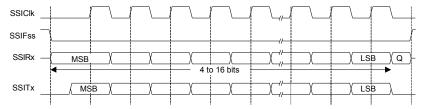

|    |      | 19.4.4.7 MICROWIRE Frame Format                              |     |

|    | 19.5 | DMA Operation                                                |     |

|    | 19.6 | Initialization and Configuration                             |     |

|    | 19.7 | SSI Registers                                                |     |

|    | 10.7 | 19.7.1 SSI Registers                                         |     |

|    |      | 19.7.1.1 SSI Registers Mapping Summary                       |     |

|    |      | 19.7.1.1.1 SSI Common Registers Mapping                      |     |

|    |      | 19.7.1.1.2 SSI Instances Register Mapping Summary            |     |

|    |      | 19.7.1.2 SSI Common Register Descriptions                    |     |

|    |      |                                                              |     |

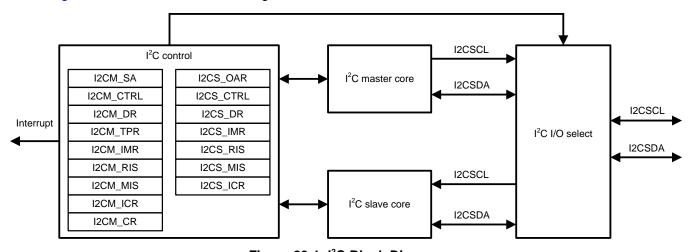

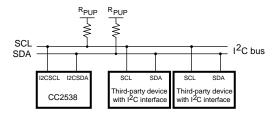

| 20 |      | -Integrated Circuit Interface                                |     |

|    | 20.1 | Inter-Integrated Circuit Interface                           |     |

|    | 20.2 | Block Diagram                                                |     |

|    | 20.3 | Functional Description                                       |     |

|    |      | 20.3.1 I <sup>2</sup> C Bus Functional Overview              |     |

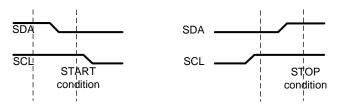

|    |      | 20.3.1.1 Start and Stop Conditions                           |     |

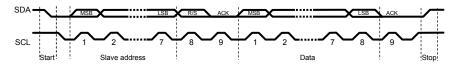

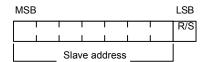

|    |      | 20.3.1.2 Data Format With 7-Bit Address                      |     |

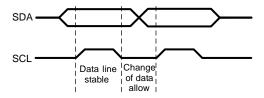

|    |      | 20.3.1.3 Data Validity                                       |     |

|    |      | 20.3.1.4 Acknowledge                                         |     |

|    |      | 20.3.1.5 Arbitration                                         |     |

|    |      | 20.3.2 Available Speed Modes                                 |     |

|    |      | 20.3.2.1 Standard and Fast Modes                             |     |

|    |      | 20.3.3 Interrupts                                            |     |

|    |      | 20.3.3.1 I <sup>2</sup> C Master Interrupts                  |     |

|    |      | 20.3.3.2 I <sup>2</sup> C Slave Interrupts                   |     |

|    |      | 20.3.4 Loopback Operation                                    |     |

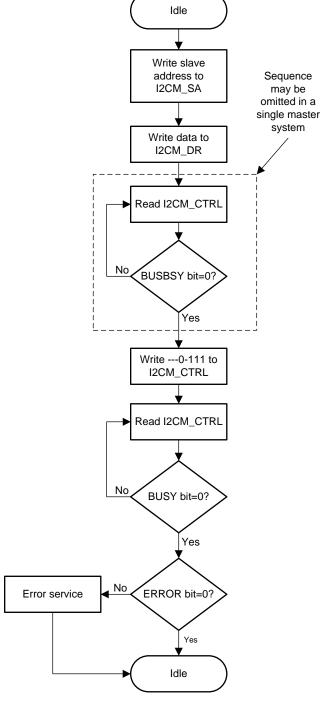

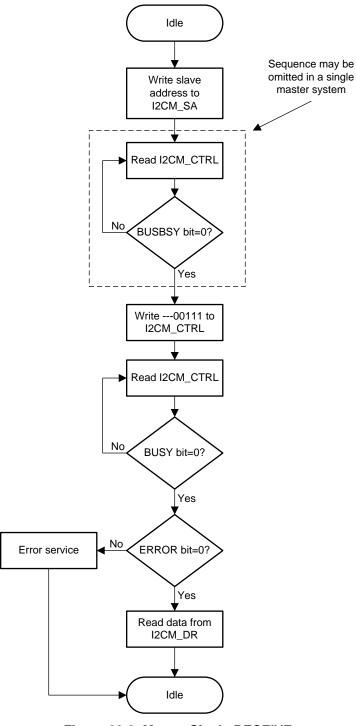

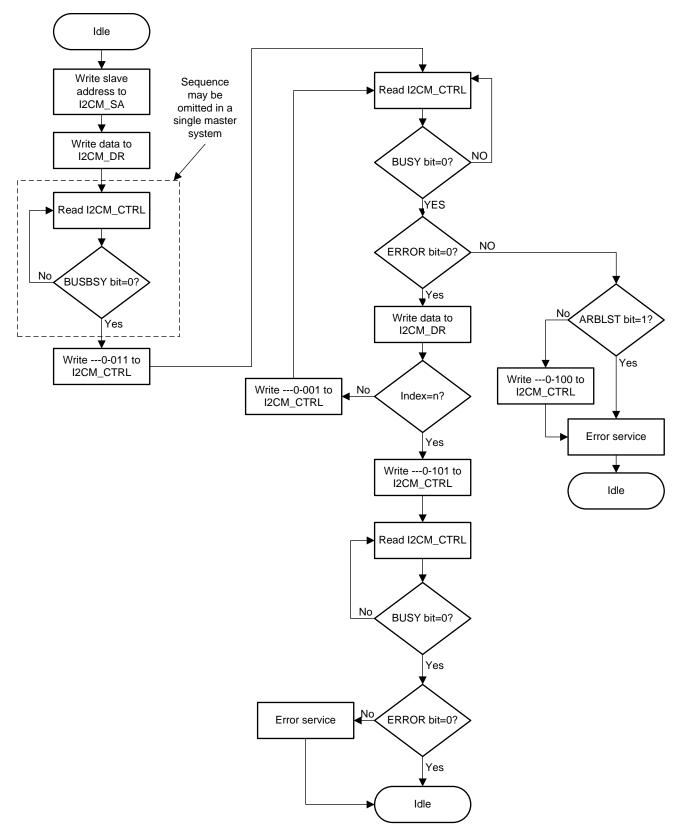

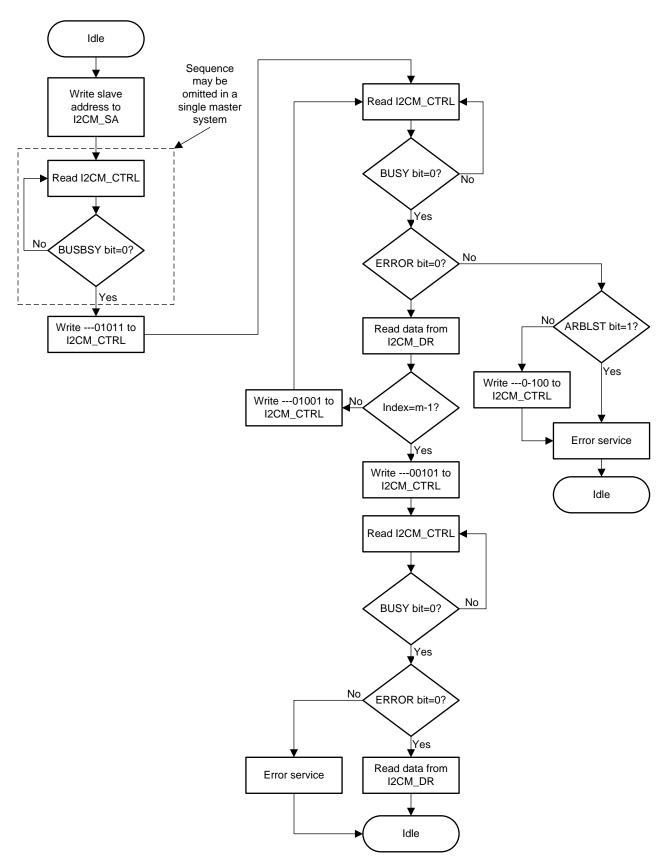

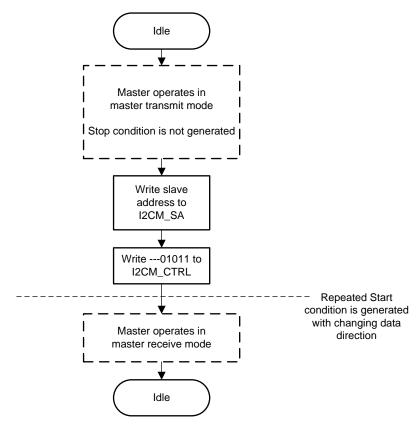

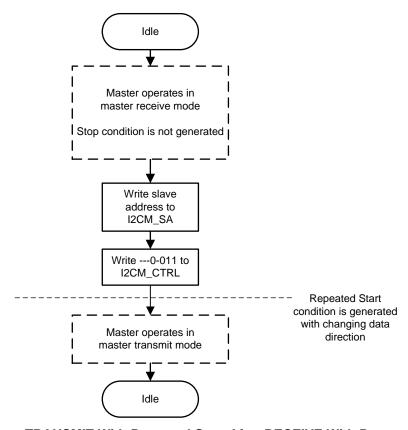

|    |      | 20.3.5 Command Sequence Flow Charts                          |     |

|    |      | 20.3.5.1 I <sup>2</sup> C Master Command Sequences           | 439 |

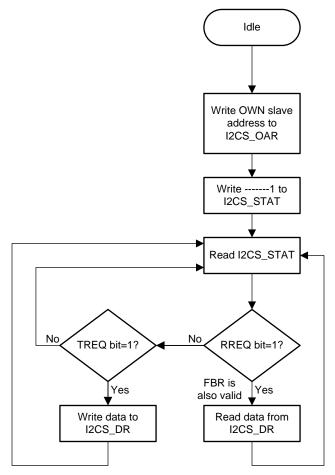

|    |       | 20.3.5.2 I <sup>2</sup> C Slave Command Sequences |     |

|----|-------|---------------------------------------------------|-----|

|    | 20.4  | Initialization and Configuration                  |     |

|    | 20.5  | I <sup>2</sup> C Registers                        |     |

|    |       | 20.5.1 I2CM Registers                             |     |

|    |       | 20.5.1.1 I2CM Registers Mapping Summary           |     |

|    |       | 20.5.1.2 I2CM Register Descriptions               | 447 |

|    |       | 20.5.2 I2CS Registers                             |     |

|    |       | 20.5.2.1 I2CS Registers Mapping Summary           | 452 |

|    |       | 20.5.2.2 I2CS Register Descriptions               | 452 |

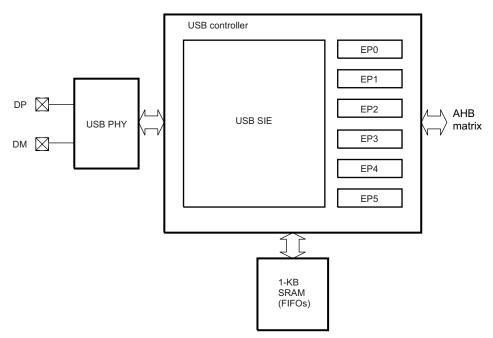

| 21 | USB ( | Controller                                        | 457 |

|    | 21.1  | USB Introduction                                  | 458 |

|    | 21.2  | USB Enable                                        | 458 |

|    | 21.3  | 48-MHz USB PLL                                    | 458 |

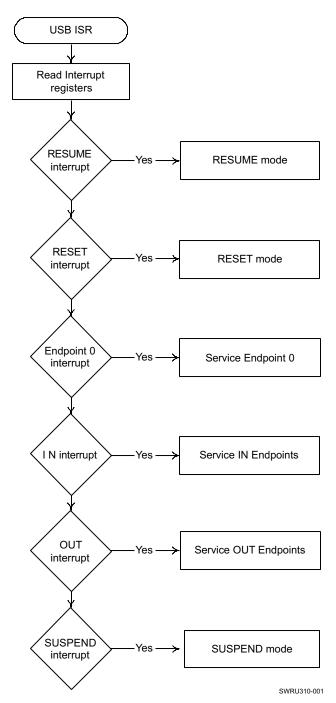

|    | 21.4  | USB Interrupts                                    | 459 |

|    | 21.5  | USB Reset                                         | 460 |

|    | 21.6  | USB Index Register                                | 461 |

|    | 21.7  | USB Suspend and Resume                            | 461 |

|    |       | 21.7.1 USB Suspend and Resume Procedure           |     |

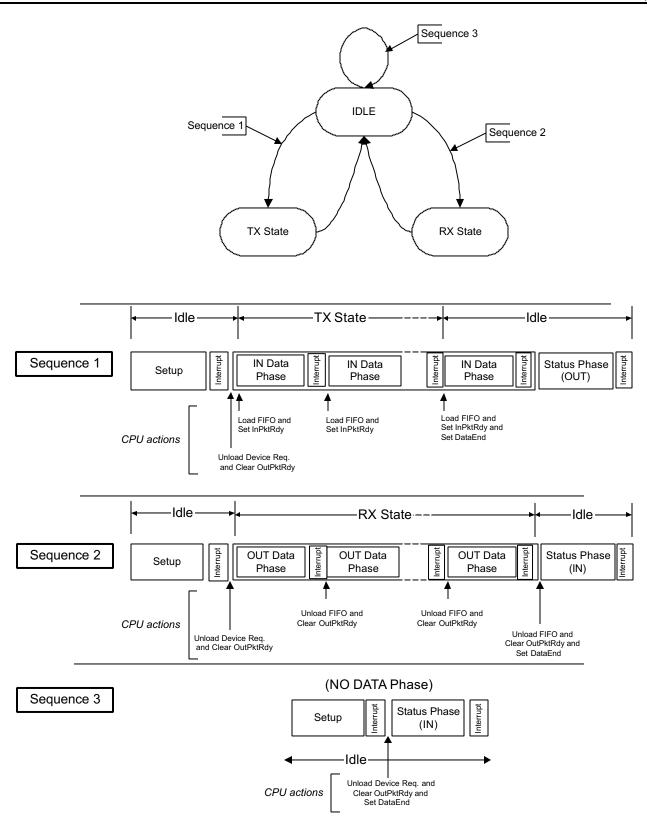

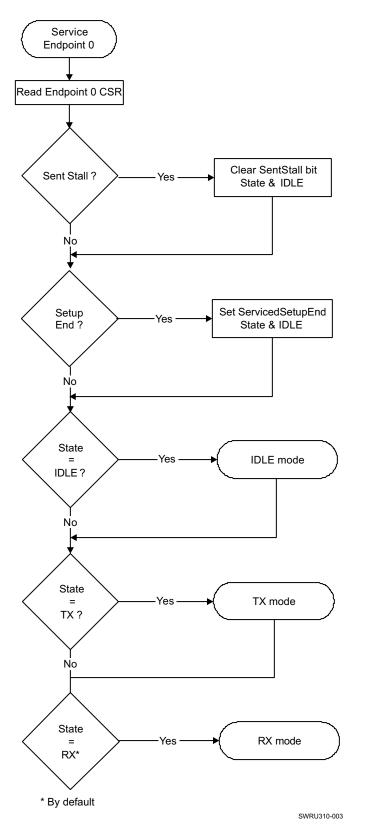

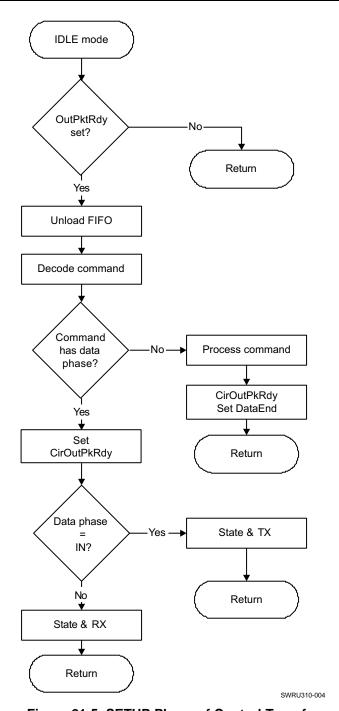

|    | 21.8  | Endpoint 0                                        |     |

|    |       | 21.8.1 Zero Data Requests                         |     |

|    |       | 21.8.2 Write Requests                             |     |

|    |       | 21.8.3 Read Requests                              |     |

|    | 21.9  | EndPoint 0 Interrupts                             |     |

|    |       | 21.9.1 Error Conditions                           | 467 |

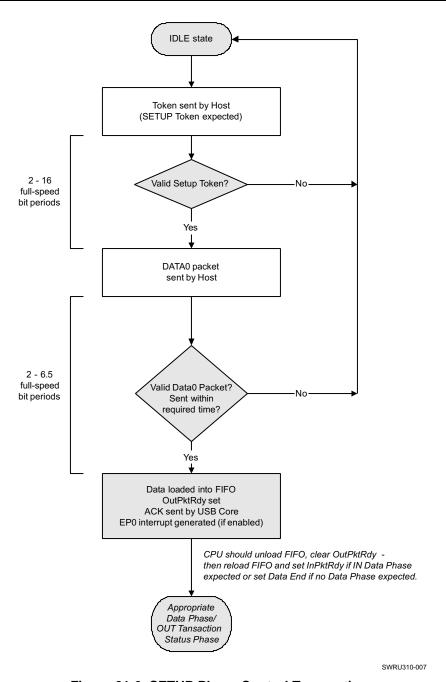

|    |       | 21.9.2 SETUP Transactions (IDLE State)            |     |

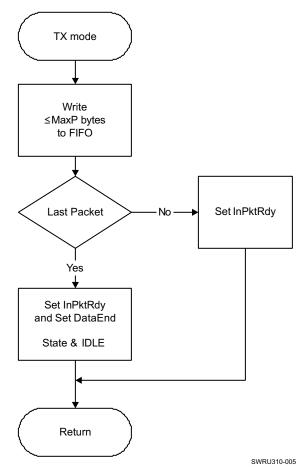

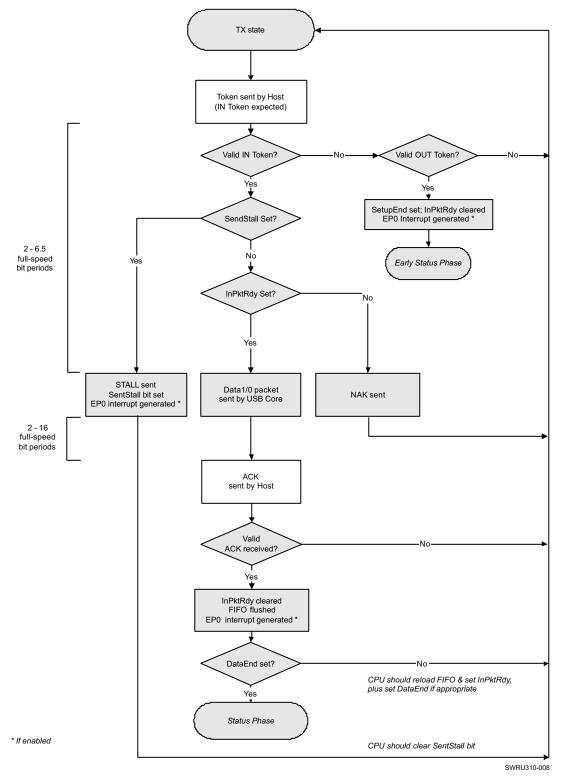

|    |       | 21.9.3 IN Transactions (TX State)                 |     |

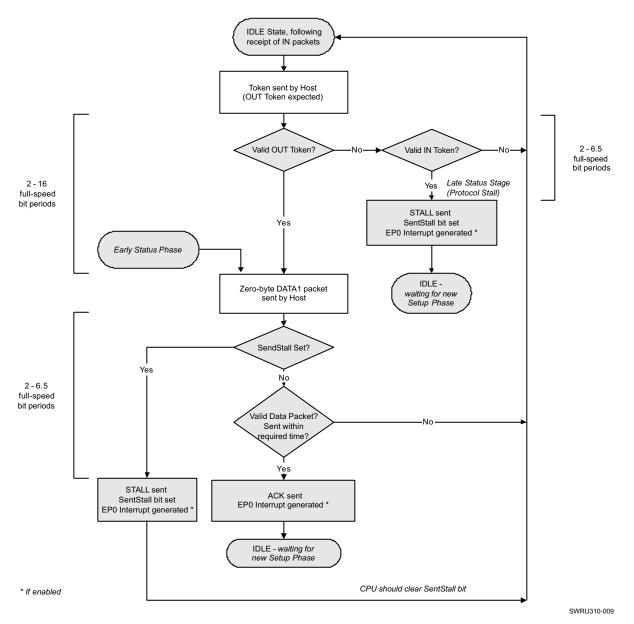

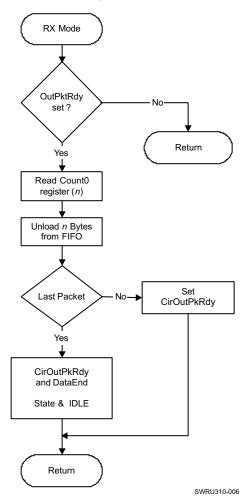

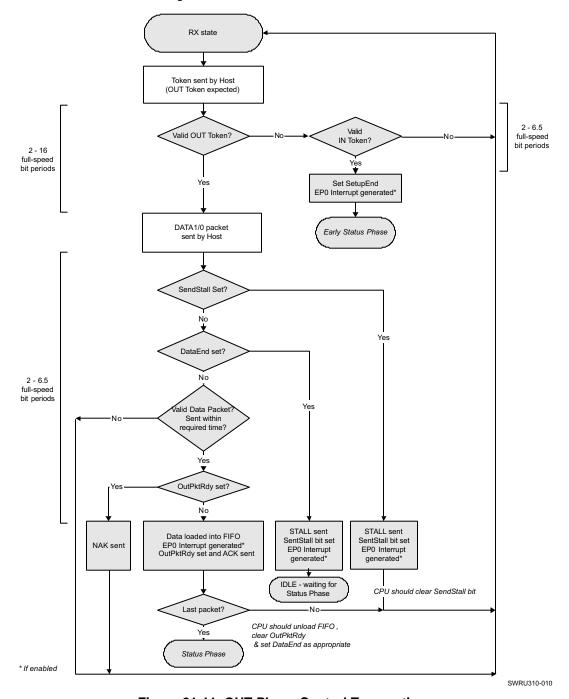

|    |       | 21.9.4 OUT Transactions (RX State)                |     |

|    | 21.10 | Endpoints 1–5                                     | 475 |

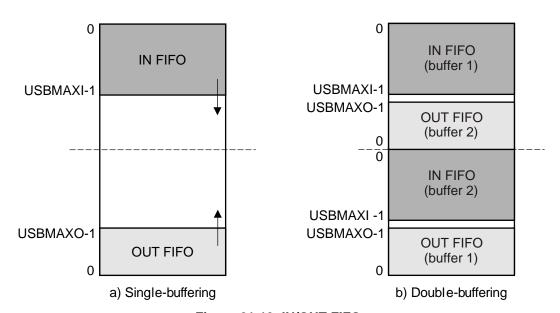

|    |       | 21.10.1 FIFO Management                           | 476 |

|    |       | 21.10.2 Double-Buffering                          | 476 |

|    |       | 21.10.3 FIFO Access                               | 477 |

|    |       | 21.10.4 Endpoint 1–5 Interrupts                   | 477 |

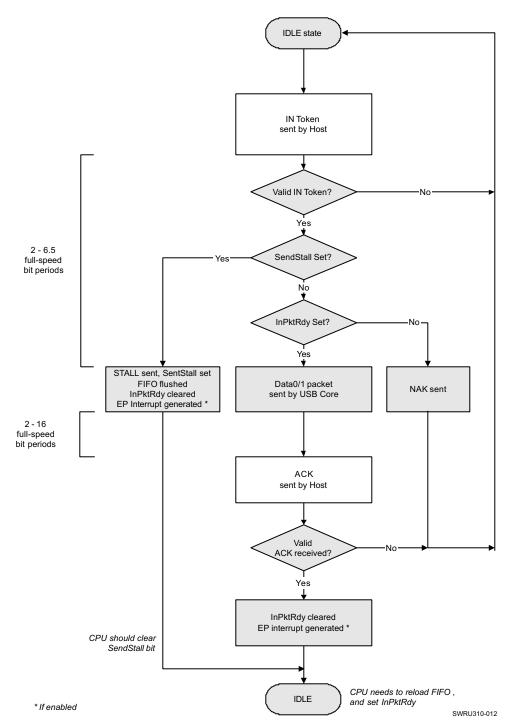

|    |       | 21.10.5 Bulk and Interrupt IN Endpoint            | 477 |

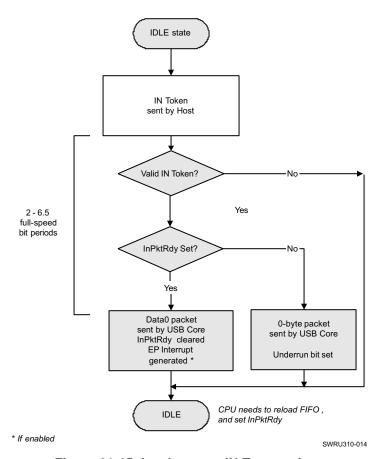

|    |       | 21.10.6 Isochronous IN Endpoint                   | 480 |

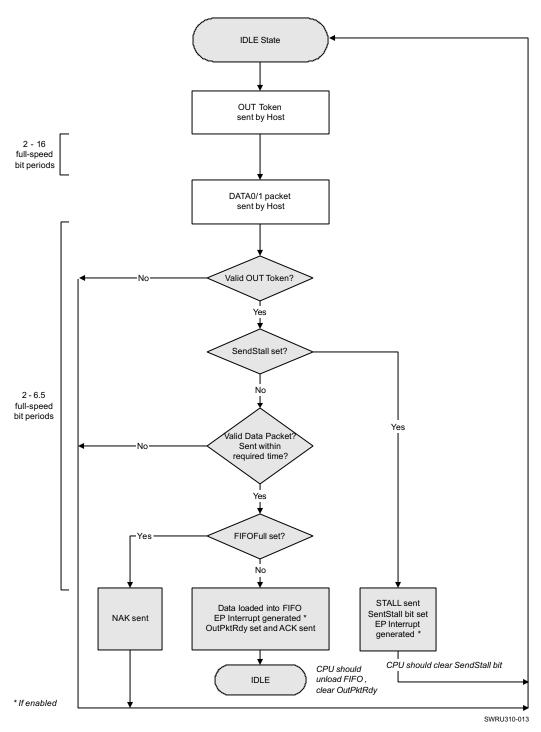

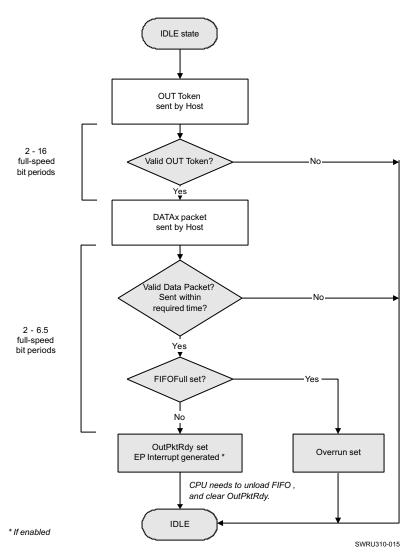

|    |       | 21.10.7 Bulk and Interrupt OUT Endpoint           | 481 |

|    |       | 21.10.8 Isochronous OUT Endpoint                  | 483 |

|    | 21.11 | DMA                                               |     |

|    | 21.12 | Remote Wake-Up                                    | 485 |

|    | 21.13 | USB Registers Overview                            | 486 |

|    | 21.14 | USB Registers                                     | 486 |

|    |       | 21.14.1 USB Registers                             | 486 |

|    |       | 21.14.1.1 USB Registers Mapping Summary           |     |

|    |       | 21.14.1.2 USB Register Descriptions               |     |

| 22 | Sacui | rity Core                                         | 500 |

|    | 22.1  | PKA Engine                                        |     |

|    | 22.1  | 22.1.1 Terms and Conventions Used in this Manual  |     |

|    |       | 22.1.1.1 Acronyms                                 |     |

|    |       | 22.1.1.2 Formulae and Nomenclature                |     |

|    |       | 22.1.2 Overview                                   |     |

|    |       | 22.1.2.1 Feature List                             |     |

|    |       | 22.1.2.2 Performance                              |     |

|    |       | 22.1.3 Functional Description                     |     |

|    |       | 22.1.3.1 Module Architecture                      |     |

|    |       | 22.1.0.1 INDUDIE AIGHREGRAFE                      | 503 |

| 22.1.3.2 PKA RAM                                                         | 503 |

|--------------------------------------------------------------------------|-----|

| 22.1.3.3 PKCP Operations                                                 | 503 |

| 22.1.3.4 Sequencer Operations                                            | 505 |

| 22.1.3.4.1 Modular Exponentiation Operations                             |     |

| 22.1.3.4.2 PKA RAM Size Needed for Exponentiation Operations             | 507 |

| 22.1.3.4.3 Modular Inversion Operation                                   | 508 |

| 22.1.3.4.4 Modular Inversion With an Even Modulus                        | 509 |

| 22.1.3.4.5 Modular Inversion With a Prime Modulus                        | 510 |

| 22.1.3.4.6 ECC Operations                                                |     |

| 22.1.4 Performance                                                       | 511 |

| 22.1.4.1 Basic PKCP Operations Performance                               |     |

| 22.1.4.2 ExpMod Performance                                              | 512 |

| 22.1.4.3 Modular Inversion Performance                                   | 514 |

| 22.1.4.4 ECC Operation Performance                                       | 514 |

| 22.1.5 Interfaces                                                        | 515 |

| 22.1.5.1 Functional Interface                                            |     |

| 22.1.5.1.1 External Interface Address Map                                | 515 |

| 22.1.5.1.2 PKA Engine Control Registers                                  | 515 |

| 22.1.5.1.3 PKA Vector_A Address (PKA_APTR)                               |     |

| 22.1.5.1.4 PKA Vector_B Address (PKA_BPTR)                               | 516 |

| 22.1.5.1.5 PKA Vector_C Address (PKA_CPTR)                               | 516 |

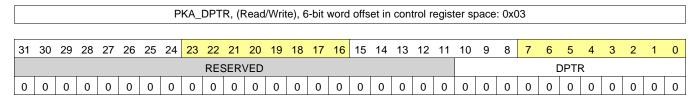

| 22.1.5.1.6 PKA Vector_D Address (PKA_DPTR)                               | 517 |

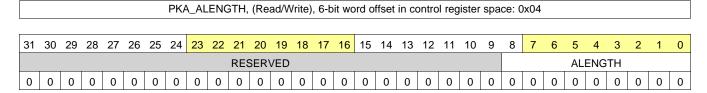

| 22.1.5.1.7 PKA Vector_A Length (PKA_ALENGTH)                             |     |

| 22.1.5.1.8 PKA Vector_B Length (PKA_BLENGTH)                             | 517 |

| 22.1.5.1.9 PKA Bit Shift Value (PKA_SHIFT)                               |     |

| 22.1.5.1.10 PKA Function (PKA_FUNCTION)                                  |     |

| 22.1.5.1.11 PKA Compare Result (PKA_COMPARE)                             |     |

| 22.1.5.1.12 PKA Most-Significant-Word of Result Vector (PKA_MSW)         |     |

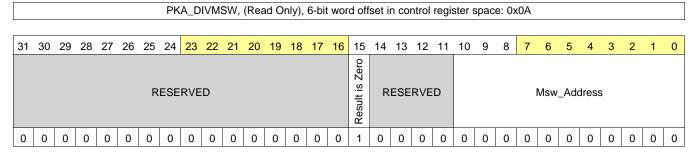

| 22.1.5.1.13 PKA Most-Significant-Word of Divide Remainder (PKA_DIVMSW)   |     |

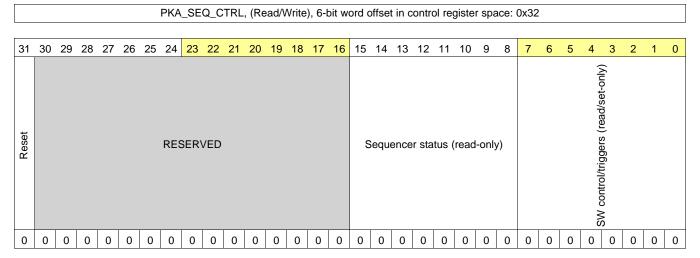

| 22.1.5.1.14 PKA Sequencer Control/Status Register (PKA_SEQ_CTRL)         |     |

| 22.1.5.1.15 PKA HW Options Register (PKA_OPTIONS)                        |     |

| 22.1.5.1.16 PKA Firmware Revision and Capabilities Register (PKA_SW_REV) |     |

| 22.1.5.1.17 PKA HW Revision Register (PKA_REVISION)                      |     |

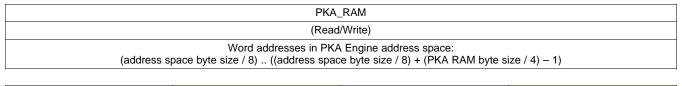

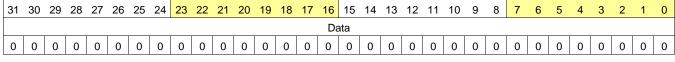

| 22.1.5.1.18 PKA Vector Ram (PKA_RAM)                                     |     |

| 22.1.5.1.19 Sequencer Program RAM (PKA_PROGRAM)                          |     |

| 22.1.5.2 Operation Sequences                                             |     |

| 22.1.6 Appendix A: RSA, ELGAMAL, DH, AND DSA Use Cases                   |     |

| 22.1.6.1 A1: RSA Use Cases                                               |     |

| 22.1.6.2 A2: Diffie-Hellman Use Cases                                    |     |

| 22.1.6.3 A3: ElGamal Use Cases                                           | 527 |

| 22.1.6.4 A4: DSA Use Cases                                               |     |

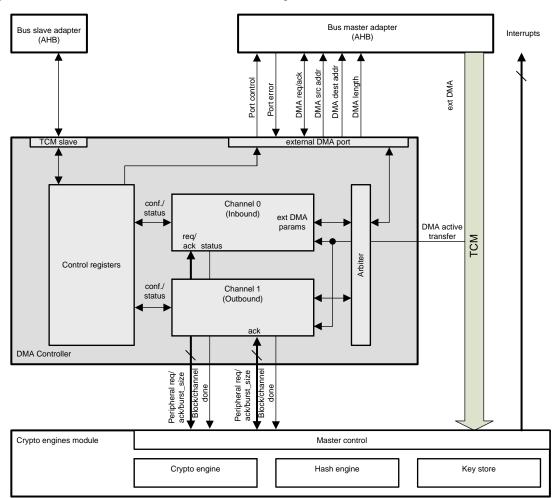

| AES and SHA Cryptoprocessor                                              |     |

| 22.2.1 Architecture Overview                                             |     |

| 22.2.1.1 Functional Description                                          |     |

| 22.2.1.1.1 Basic DMA Controller With AHB Master Interface                | 529 |

| 22.2.1.1.2 Key Store                                                     | 529 |

| 22.2.1.1.3 AES Crypto Engine                                             |     |

| 22.2.1.1.4 SHA-256 Hash Engine                                           |     |

| 22.2.1.1.5 Master Control and Interrupts                                 |     |

| 22.2.1.1.6 Debug Capabilities                                            |     |

| 22.2.1.1.7 Exception Handling                                            |     |

| 22.2.2 Hardware Description                                              |     |

| 22.2.2.1 Slave Bus                                                       | 530 |

22.2

|               | Functional Description                                                |     |

|---------------|-----------------------------------------------------------------------|-----|

| 22.2.2.1.2    | Endianness                                                            | 530 |

| 22.2.2.1.3    | Performance                                                           | 530 |

| 22.2.2.2 Ma   | ster Bus                                                              | 531 |

| 22.2.2.3 Inte | errupts                                                               | 531 |

| 22.2.3 Module | Description                                                           | 531 |

| 22.2.3.1 Intr | oduction                                                              | 531 |

| 22.2.3.2 Gld  | obal and Detailed Memory Map                                          | 531 |

| 22.2.3.3 DM   | IA Controller                                                         | 534 |

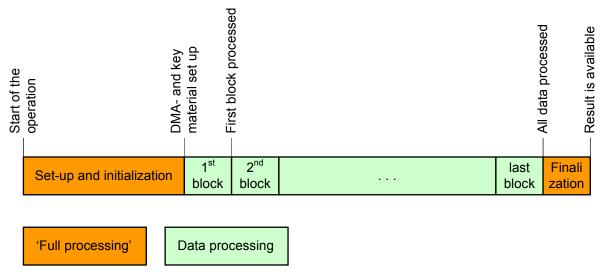

| 22.2.3.3.1    | Operation                                                             | 534 |

| 22.2.3.3.2    | Channels and Arbiter                                                  | 536 |

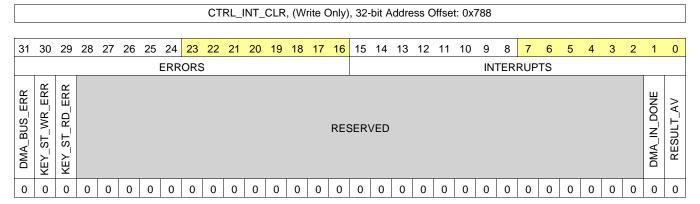

| 22.2.3.3.3    | Control/Status Registers                                              | 538 |

| 22.2.3.4 Ma   | ster Control and Select                                               | 541 |

|               | Algorithm Select                                                      |     |

|               | Master PROT Enable                                                    |     |

|               | Software Reset                                                        |     |

| 22.2.3.4.4    | Interrupt                                                             |     |

| 22.2.3.4.5    | ·                                                                     |     |

|               | S Engine                                                              |     |

|               | Second Key / GHASH Key (internal, but clearable)                      |     |

|               | AES Key Registers (internal)                                          |     |

| 22.2.3.5.3    | AES Initialization Vector Registers                                   |     |

| 22.2.3.5.4    | ES Input/Output Buffer Control & Mode Register                        |     |

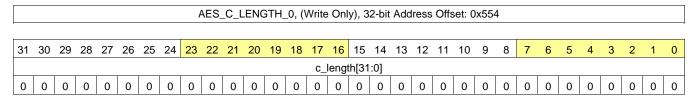

| 22.2.3.5.5    | AES Crypto Length Registers                                           |     |

| 22.2.3.5.6    | Authentication Length Register                                        |     |

| 22.2.3.5.7    | Data Input/Output Registers                                           |     |

|               | TAG Registers                                                         |     |

|               | SH Core                                                               |     |

| 22.2.3.6.1    | Introduction                                                          |     |

| 22.2.3.6.2    | Data Input Registers                                                  |     |

| 22.2.3.6.3    | Input/Output Buffer Control & Status Register                         |     |

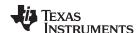

| 22.2.3.6.4    | Mode Registers                                                        |     |

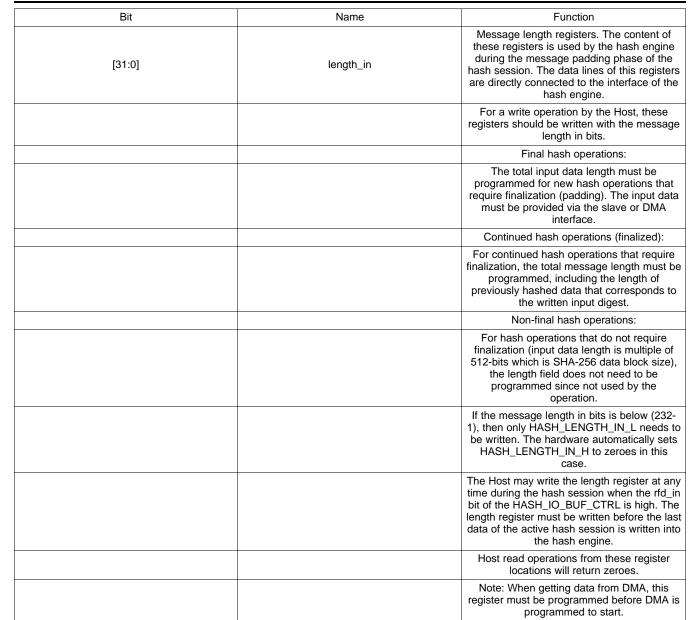

| 22.2.3.6.5    | Length Registers                                                      |     |

| 22.2.3.6.6    | Hash Digest Registers                                                 |     |

|               | y Store                                                               |     |

| 22.2.3.7 Re   |                                                                       |     |

| -             | Key Store Written Area Register                                       |     |

|               | · ·                                                                   | 566 |

| 22.2.3.7.3    | ·, · · · · · · · · · · · · · · · · · ·                                | 567 |

|               | Key Store Read Area Register                                          | 567 |

|               | nance                                                                 | 568 |

|               | roduction                                                             | 568 |

|               | formance                                                              | 569 |

|               | nming Guidelines                                                      | 569 |

|               | e Time Initialization After a Reset                                   |     |

|               | IAC and Master Control                                                | 570 |

| 22.2.5.2.1    | Regular use                                                           | 570 |

| 22.2.5.2.2    | Interrupting DMA Transfers                                            | 570 |

| 22.2.5.2.3    | Interrupts and HW/SW Synchronization                                  | 571 |

|               | shing                                                                 | 571 |

| 22.2.5.3.1    | Data Format and Byte Order                                            | 571 |

|               | Basic Hash With Data From the DMA                                     |     |

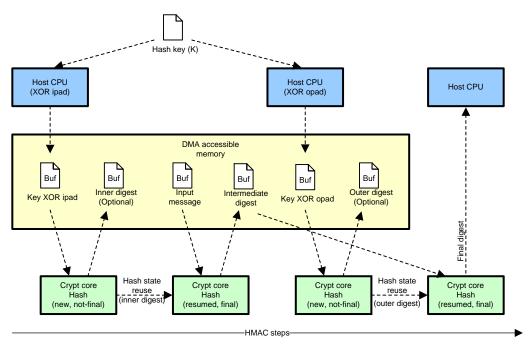

| 22.2.5.3.3    |                                                                       |     |

| 22.2.5.3.4    | Alternative Basic Hash Where Data Originates From the Slave Interface | 575 |

|    |       | 22.2.5.4 Encryption/Decryption                                 | 577 |

|----|-------|----------------------------------------------------------------|-----|

|    |       | 22.2.5.4.1 Data Format and Byte Order                          |     |

|    |       | 22.2.5.4.2 Key Store                                           |     |

|    |       | 22.2.5.4.3 Basic AES Modes                                     |     |

|    |       | 22.2.5.4.4 AES-GCM                                             |     |

|    |       | 22.2.5.4.5 CBC-MAC                                             |     |

|    |       | 22.2.5.4.6 AES-CCM                                             |     |

|    |       | 22.2.5.5 Exceptions Handling                                   |     |

|    |       | 22.2.5.5.1 Soft Reset                                          |     |

|    |       |                                                                |     |

|    |       | 22.2.5.5.2 External Port Errors                                |     |

|    |       | 22.2.5.5.3 Key Store Errors                                    |     |

|    |       | 22.2.6 Conventions and Compliances                             |     |

|    |       | 22.2.6.1 Conventions Used in This Manual                       |     |

|    |       | 22.2.6.1.1 Acronyms                                            |     |

|    |       | 22.2.6.1.2 Terminology                                         |     |

|    |       | 22.2.6.1.3 Formulae and Nomenclature                           | 586 |

|    |       | 22.2.6.1.4 Register Information                                | 587 |

|    |       | 22.2.6.2 Compliances                                           | 587 |

|    | 22.3  | Public Key Processor                                           | 588 |

|    |       | 22.3.1 Advanced Interrupt Controller                           | 588 |

|    |       | 22.3.2 Registers                                               |     |

|    |       | 22.3.2.1 Register Address Map                                  |     |

|    |       | 22.3.2.2 Register Description                                  |     |

|    |       | 22.3.2.2.1 Engine Registers                                    |     |

|    |       | 22.3.3 Advanced Interrupt Controller (Optional)                |     |

|    |       | 22.3.3.1 Introduction                                          |     |

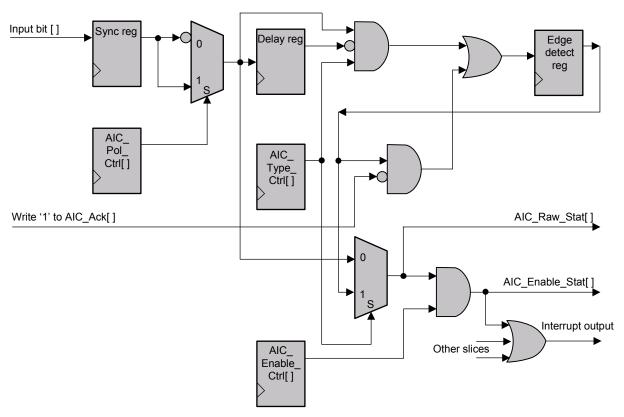

|    |       | 22.3.3.2 Functional Description                                |     |

|    |       | 22.3.3.3 Interrupt Sources                                     |     |

|    |       | •                                                              |     |

|    |       | 22.3.3.4 AIC Registers                                         |     |

|    |       | 22.3.3.4.1 AIC Polarity Control Register (AIC_POL_CTRL)        |     |

|    |       | 22.3.3.4.2 AIC Type Control Register (AIC_TYPE_CTRL)           |     |

|    |       | 22.3.3.4.3 4.4.3 AIC Enable Control Register (AIC_ENABLE_CTRL) |     |

|    |       | 22.3.3.4.4 AIC Raw Source Status Register (AIC_RAW_STAT)       |     |

|    |       | 22.3.3.4.5 AIC Enabled Status Register (AIC_ENABLED_STAT)      |     |

|    |       | 22.3.3.4.6 AIC Acknowledge Register (AIC_ACK)                  |     |

|    |       | 22.3.3.4.7 AIC Enable Set Register (AIC_ENABLE_SET)            | 595 |

|    |       | 22.3.3.4.8 AIC Enable Clear Register (AIC_ENABLE_CLR)          | 595 |

|    |       | 22.3.3.4.9 AIC Options Register (AIC_OPTIONS)                  | 596 |

|    |       | 22.3.3.4.10 AIC Version Register (AIC_VERSION)                 | 596 |

|    | 22.4  | AES and PKA Registers                                          | 597 |

|    |       | 22.4.1 AES Registers                                           | 597 |

|    |       | 22.4.1.1 AES Registers Mapping Summary                         | 597 |

|    |       | 22.4.1.2 AES Register Descriptions                             |     |

|    |       | 22.4.2 PKA Registers                                           |     |

|    |       | 22.4.2.1 PKA Registers Mapping Summary                         |     |

|    |       | 22.4.2.2 PKA Register Descriptions                             |     |

| 00 | Dadia |                                                                |     |

| 23 |       | )                                                              | 659 |

|    | 23.1  | RF Core                                                        |     |

|    |       | 23.1.1 Interrupts                                              |     |

|    |       | 23.1.2 Interrupt Registers                                     |     |

|    | 23.2  | FIFO Access                                                    | 661 |

|    | 23.3  | DMA                                                            | 661 |

|    | 23.4  | Memory Map                                                     | 661 |

|    |       |                                                                |     |

|       | 23.4.1 RX FIFO                                                   | 661 |

|-------|------------------------------------------------------------------|-----|

|       | 23.4.2 TX FIFO                                                   | 661 |

|       | 23.4.3 Frame-Filtering and Source-Matching Memory Map            | 662 |

| 23.5  | Frequency and Channel Programming                                | 663 |

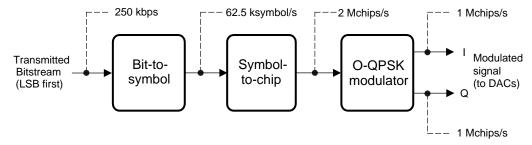

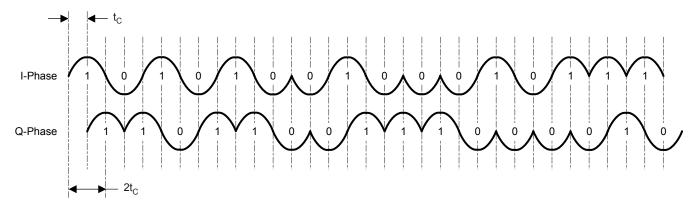

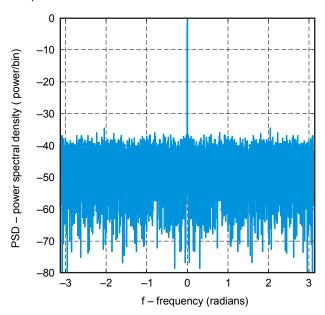

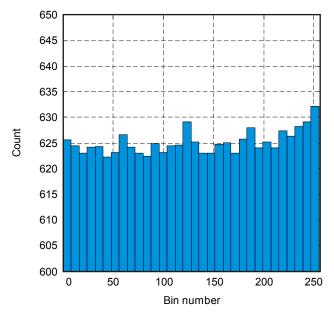

| 23.6  | IEEE 802.15.4-2006 Modulation Format                             | 664 |

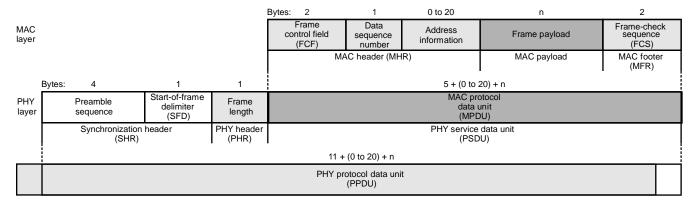

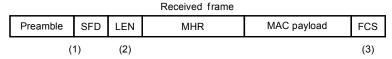

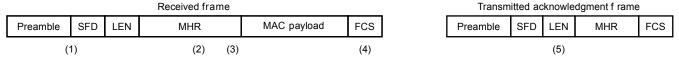

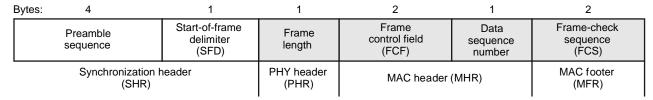

| 23.7  | IEEE 802.15.4-2006 Frame Format                                  | 665 |

|       | 23.7.1 PHY Layer                                                 | 665 |

|       | 23.7.2 MAC Layer                                                 | 666 |

| 23.8  | Transmit Mode                                                    | 666 |

|       | 23.8.1 TX Control                                                | 666 |

|       | 23.8.2 TX State Timing                                           | 667 |

|       | 23.8.3 TX FIFO Access                                            | 667 |

|       | 23.8.4 Retransmission                                            | 667 |

|       | 23.8.5 Error Conditions                                          | 667 |

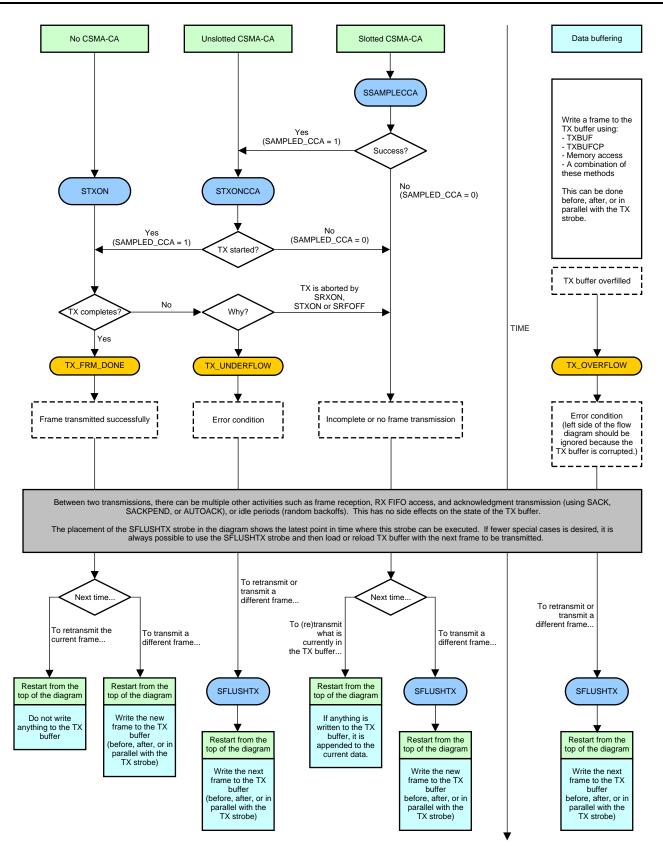

|       | 23.8.6 TX Flow Diagram                                           |     |

|       | 23.8.7 Frame Processing                                          |     |

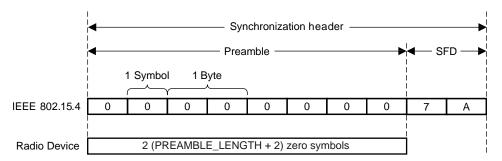

|       | 23.8.8 Synchronization Header                                    |     |

|       | 23.8.9 Frame-Length Field                                        |     |

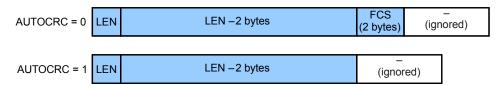

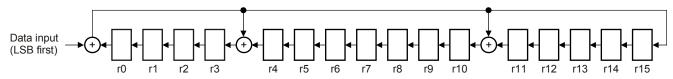

|       | 23.8.10 Frame-Check Sequence                                     |     |

|       | 23.8.11 Interrupts                                               |     |

|       | 23.8.12 Clear-Channel Assessment                                 |     |

|       | 23.8.13 Output Power Programming                                 |     |

|       | 23.8.14 Tips and Tricks                                          |     |

| 23.9  | Receive Mode                                                     |     |

|       | 23.9.1 RX Control                                                |     |

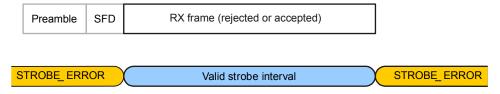

|       | 23.9.2 RX State Timing                                           |     |

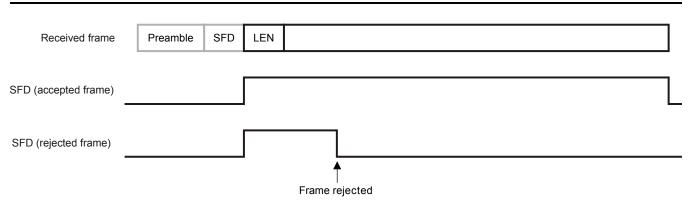

|       | 23.9.3 Frame Processing                                          |     |

|       | 23.9.4 Synchronization Header and Frame-Length Fields            |     |

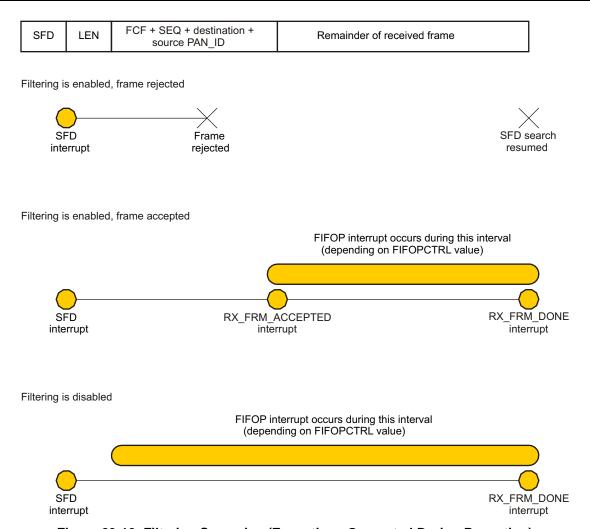

|       | 23.9.5 Frame Filtering                                           |     |

|       | 23.9.5.1 Filtering Algorithm                                     |     |

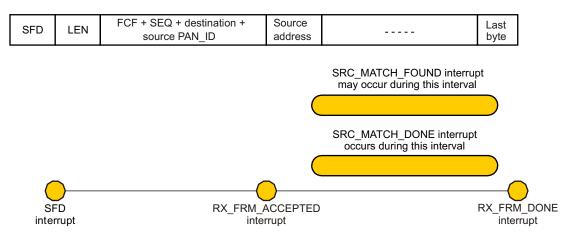

|       | 23.9.5.2 Interrupts                                              |     |

|       | 23.9.5.3 Tips and Tricks                                         |     |

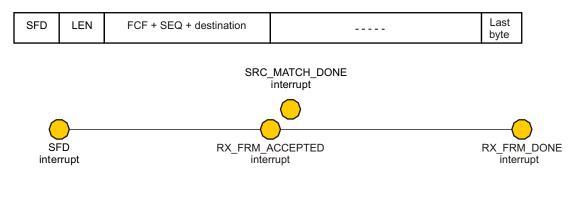

|       | 23.9.6 Source Address Matching                                   |     |

|       | 23.9.6.1 Applications                                            |     |

|       | 23.9.6.2 The Source Address Table                                |     |

|       | 23.9.6.3 Address Enable Registers                                |     |

|       | 23.9.6.4 Matching Algorithm                                      | 677 |

|       | 23.9.6.5 Interrupts                                              | 678 |

|       | 23.9.6.6 Tips and Tricks                                         |     |

|       | 23.9.7 Frame-Check Sequence                                      |     |

|       | 23.9.8 Acknowledgement Transmission                              |     |

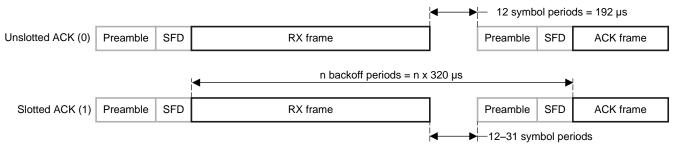

|       | 23.9.8.1 Transmission Timing                                     |     |

|       | 23.9.8.2 Manual Control                                          |     |

|       | 23.9.8.3 Automatic Control (AUTOACK)                             |     |

|       | 23.9.8.4 Automatic Setting of the Frame Pending Field (AUTOPEND) |     |

| 23 10 | RX FIFO Access                                                   | 681 |

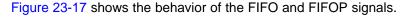

| _0.10 | 23.10.1 Using the FIFO and FIFOP Signals                         |     |

|       | 23.10.2 Error Conditions                                         |     |

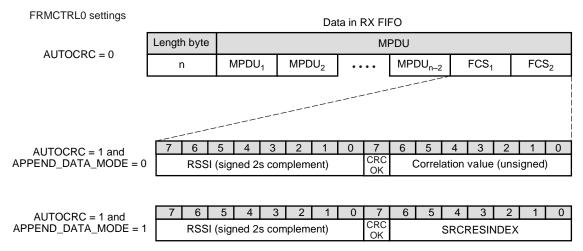

|       | 23.10.3 RSSI                                                     | 682 |

|       | 23.10.4 Link Quality Indication                                  | 683 |

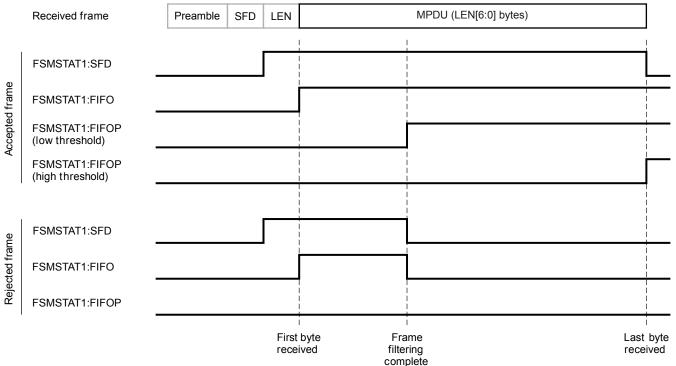

| 23.11 | Radio Control State-Machine                                      | 683 |

| 23.12 | Random Number Generation                                         | 685 |

| 23.13 |                                                                  |     |

| 9     | 9 · · · · · · · · · · · · · · · · · · ·                          |     |

| 23.14 |              | trobe/CSMA-CA Processor |      |

|-------|--------------|-------------------------|------|

|       |              | truction Memory         |      |

|       |              | a Registers             |      |

|       |              | gram Execution          |      |

|       | 23.14.4 Inte | errupt Requests         | 688  |

|       | 23.14.5 Rar  | ndom Number Instruction | 688  |

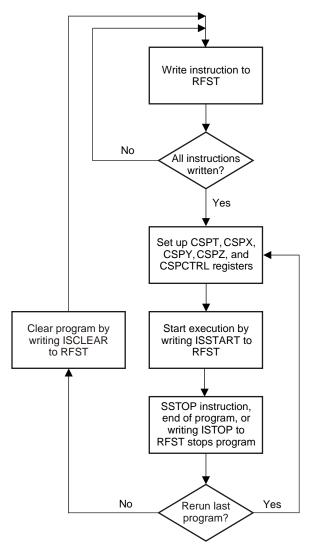

|       | 23.14.6 Rur  | nning CSP Programs      | 688  |

|       | 23.14.7 CS   | P Registers             | 689  |

|       | 23.14.8 Inst | truction Set Summary    | 690  |

|       | 23.14.9 Inst | truction Set Definition | 691  |

|       | 23.14.9.1    | DECZ                    | 691  |

|       | 23.14.9.2    | DECY                    | 692  |

|       | 23.14.9.3    | DECX                    | 692  |

|       | 23.14.9.4    | INCZ                    | 692  |

|       | 23.14.9.5    | INCY                    | 692  |

|       | 23.14.9.6    | INCX                    | 692  |

|       | 23.14.9.7    | INCMAXY                 | 693  |

|       | 23.14.9.8    | RANDXY                  | 693  |

|       | 23.14.9.9    | INT                     | 693  |

|       | 23.14.9.10   | WAITX                   | 693  |

|       | 23.14.9.11   | SETCMP1                 | 694  |

|       | 23.14.9.12   | WAIT W                  | 694  |

|       | 23.14.9.13   | WEVENT1                 | 694  |

|       | 23.14.9.14   | WEVENT2                 | 695  |

|       | 23.14.9.15   | LABEL                   | 695  |

|       | 23.14.9.16   | RPT C                   | 695  |

|       | 23.14.9.17   | SKIP S, C               | 696  |

|       | 23.14.9.18   | STOP                    | 696  |

|       | 23.14.9.19   | SNOP                    | 697  |

|       | 23.14.9.20   | SRXON                   | 697  |

|       | 23.14.9.21   | STXON                   | 697  |

|       | 23.14.9.22   | STXONCCA                | 697  |

|       | 23.14.9.23   | SSAMPLECCA              | 698  |

|       | 23.14.9.24   | SRFOFF                  | 698  |

|       | 23.14.9.25   | SFLUSHRX                | 698  |

|       | 23.14.9.26   | SFLUSHTX                | 698  |

|       | 23.14.9.27   | SACK                    | 698  |

|       | 23.14.9.28   | SACKPEND                | 699  |

|       | 23.14.9.29   | SNACK                   | 699  |

|       | 23.14.9.30   | SRXMASKBITSET           | 699  |

|       | 23.14.9.31   | SRXMASKBITCLR           | 699  |

|       | 23.14.9.32   | ISSTOP                  | 700  |

|       | 23.14.9.33   | ISSTART                 | 700  |

|       | 23.14.9.34   | ISRXON                  | 700  |

|       | 23.14.9.35   | ISRXMASKBITSET          | 700  |

|       | 23.14.9.36   | ISRXMASKBITCLR          |      |

|       | 23.14.9.37   |                         |      |

|       | 23.14.9.38   |                         |      |

|       |              | ISSAMPLECCA             |      |

|       | 23.14.9.40   |                         |      |

|       | 23.14.9.41   |                         | _    |

|       |              | ISFLUSHTX               | _    |

|       |              | ISACK                   |      |

|       | _30.70       |                         | . 5- |

|    | 23.14.9.44 ISACKPEND                                                   | . 702 |

|----|------------------------------------------------------------------------|-------|

|    | 23.14.9.45 ISNACK                                                      | . 703 |

|    | 23.14.9.46 ISCLEAR                                                     | . 703 |

|    | 23.15 Register Settings Update                                         | . 703 |

|    | 23.16 Radio Registers                                                  | . 704 |

|    | 23.16.1 RFCORE_FFSM Registers                                          | . 704 |

|    | 23.16.1.1 RFCORE_FFSM Registers Mapping Summary                        | . 704 |

|    | 23.16.1.2 RFCORE_FFSM Register Descriptions                            | . 705 |

|    | 23.16.2 RFCORE_XREG Registers                                          |       |

|    | 23.16.2.1 RFCORE_XREG Registers Mapping Summary                        | . 712 |

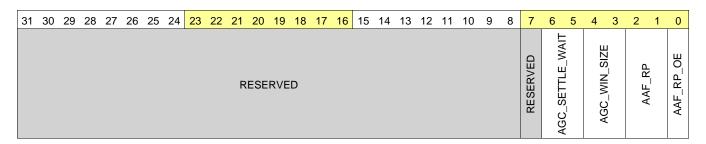

|    | 23.16.2.2 RFCORE_XREG Register Descriptions                            | . 715 |

|    | 23.16.3 RFCORE_SFR Registers                                           |       |

|    | 23.16.3.1 RFCORE_SFR Registers Mapping Summary                         | . 749 |

|    | 23.16.3.2 RFCORE_SFR Register Descriptions                             |       |

|    | 23.16.4 CCTEST Registers                                               |       |

|    | 23.16.4.1 CCTEST Registers Mapping Summary                             |       |

|    | 23.16.4.2 CCTEST Register Descriptions                                 |       |

|    | 23.16.5 ANA_REGS Registers                                             |       |

|    | 23.16.5.1 ANA_REGS Registers Mapping Summary                           |       |

|    | 23.16.5.2 ANA_REGS Register Descriptions                               | . 757 |

| 24 | Voltage Regulator                                                      | 759   |

| Α  | Available Software                                                     | 760   |

|    | A.1 SmartRF™ Studio Software for Evaluation (www.ti.com/smartrfstudio) |       |

|    | A.2 TIMAC Software (www.ti.com/timac)                                  |       |

|    | A.3 Z-Stack™ Software (www.ti.com/z-stack)                             |       |

| В  | Abbreviations                                                          |       |

|    |                                                                        |       |

| С  | Additional Information                                                 |       |

|    | C.1 Texas Instruments Low-Power RF Web Site                            |       |

|    | C.2 Low-Power RF Online Community                                      |       |

|    | C.3 Texas Instruments Low-Power RF Developer Network                   |       |

|    | C.4 Low-Power RF eNewsletter                                           |       |

| D  | References                                                             | 768   |

| Ε  | Revision History                                                       | 769   |

|    | E.1 Revision History – External                                        |       |

# **List of Figures**

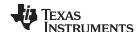

| 1-1.  | CC2538 Block Diagram                                             | 34  |

|-------|------------------------------------------------------------------|-----|

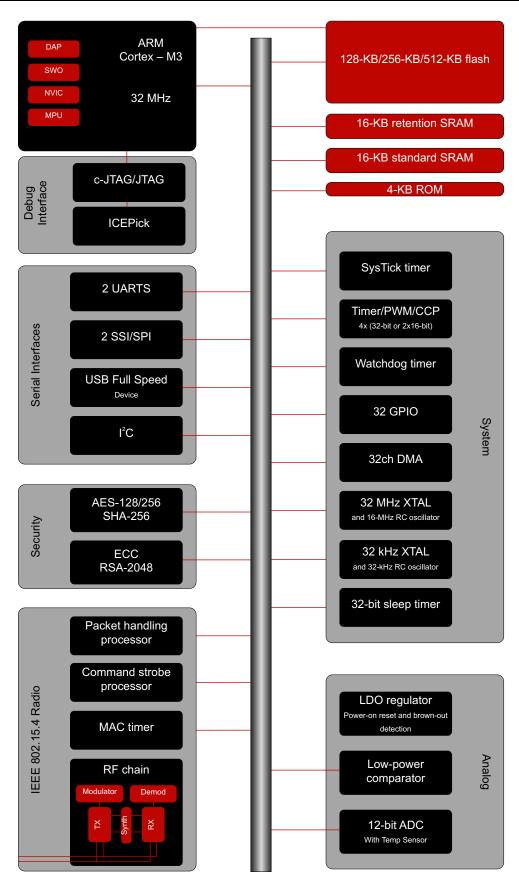

| 2-1.  | CPU Block Diagram                                                | 47  |

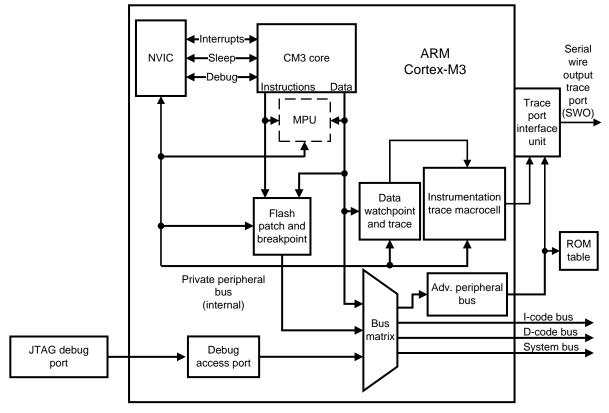

| 2-2.  | TPIU Block Diagram                                               | 48  |

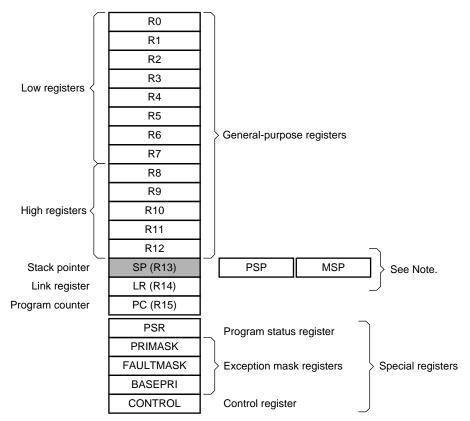

| 2-3.  | Cortex-M3 Register Set                                           | 50  |

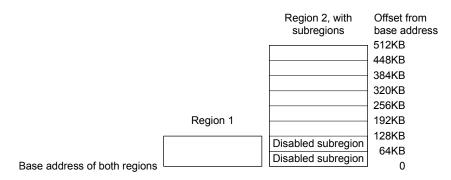

| 3-1.  | SRD Use Example                                                  | 71  |

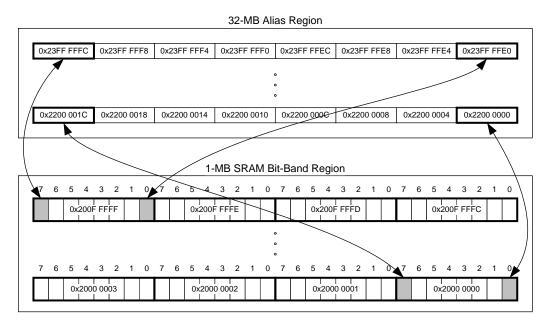

| 4-1.  | Bit-Band Mapping                                                 | 161 |

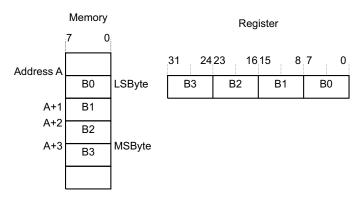

| 4-2.  | Data Storage                                                     | 162 |

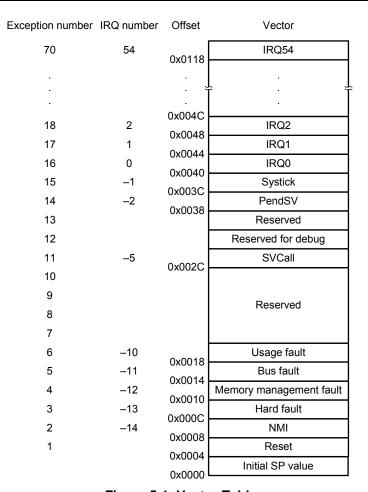

| 5-1.  | Vector Table                                                     | 171 |

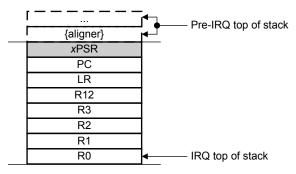

| 5-2.  | Exception Stack Frame                                            | 173 |

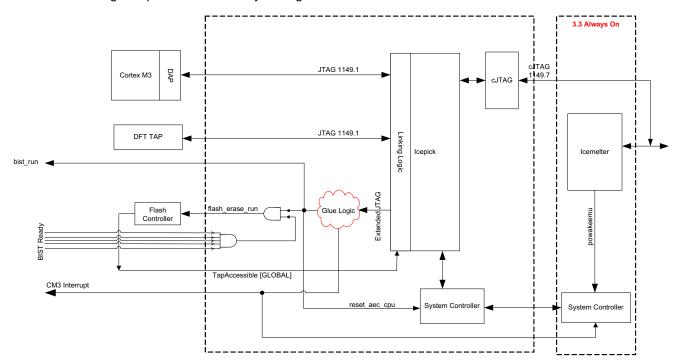

| 6-1.  | Test/Debug System Top Level Diagram                              | 178 |

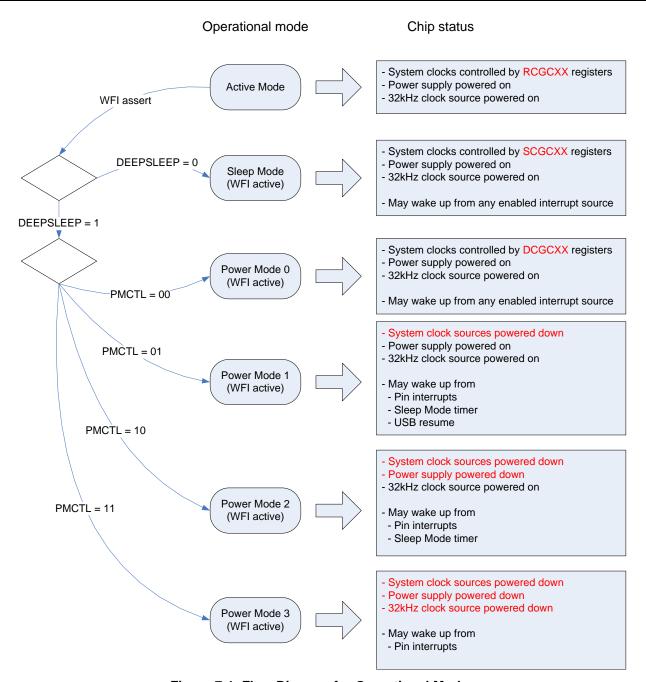

| 7-1.  | Flow Diagram for Operational Modes                               | 186 |

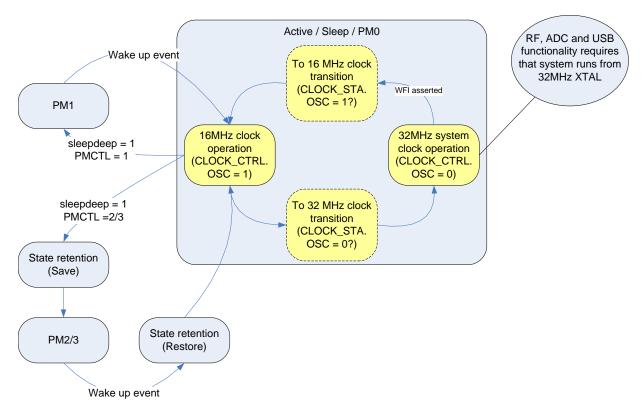

| 7-2.  | Simple Flow Diagram for Power Management                         | 188 |

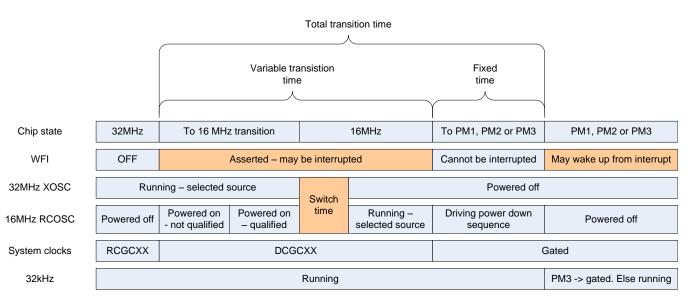

| 7-3.  | Timing Example for Transition from 32 MHz to PM's                | 190 |

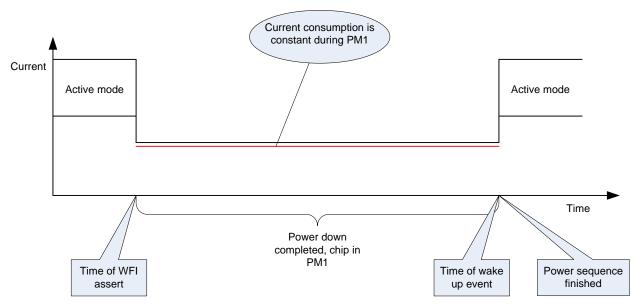

| 7-4.  | Simplified Figure of Current Consumption in PM1                  | 192 |

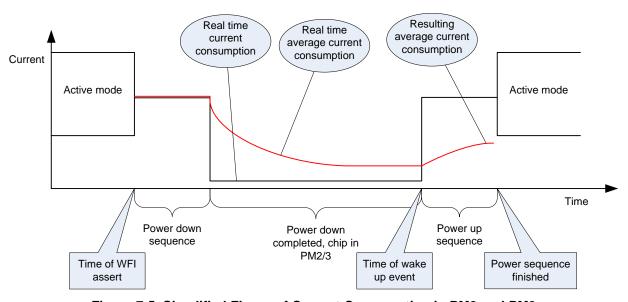

| 7-5.  | Simplified Figure of Current Consumption in PM2 and PM3          | 192 |

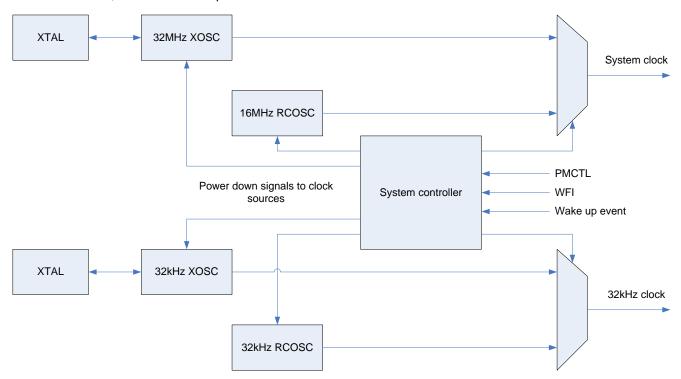

| 7-6.  | Block Diagram Oscillators and Clocks                             | 193 |

| 8-1.  | Flash Write Using DMA                                            | 218 |

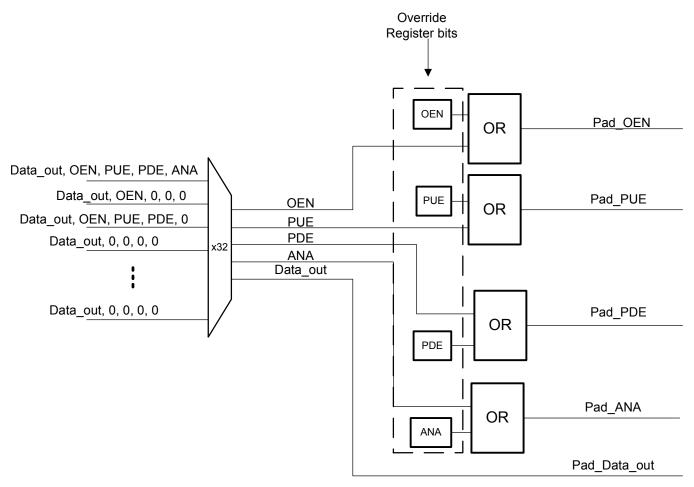

| 9-1.  | Digital I/O Pads (The Diagram Shows One of 32 Possible I/O Pins) | 233 |

| 9-2.  | GPIODATA Write Example                                           | 234 |

| 9-3.  | GPIODATA Read Example                                            | 234 |

| 9-4.  | PAD Configuration Override Registers                             | 237 |

| 10-1. | μDMA Block Diagram                                               | 287 |

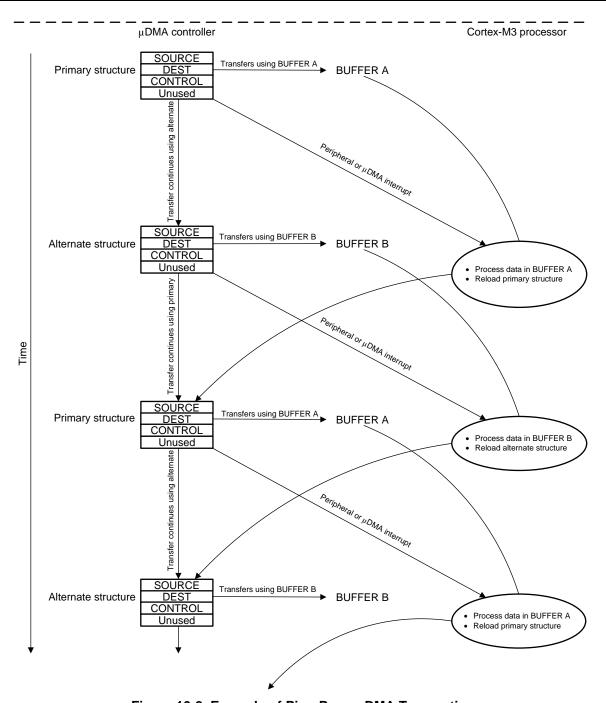

| 10-2. | Example of Ping-Pong µDMA Transaction                            | 293 |

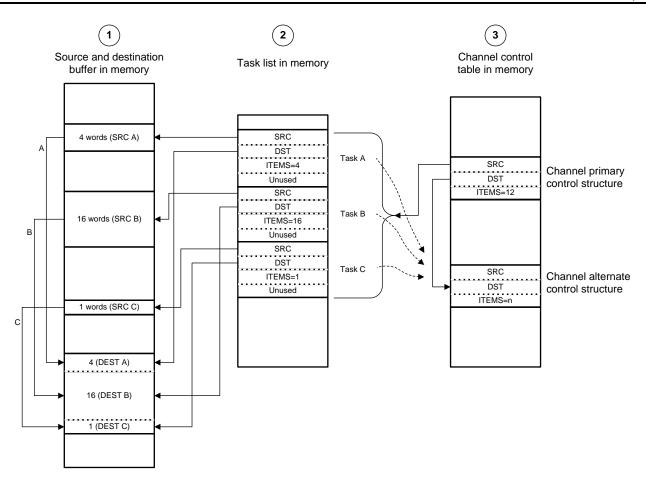

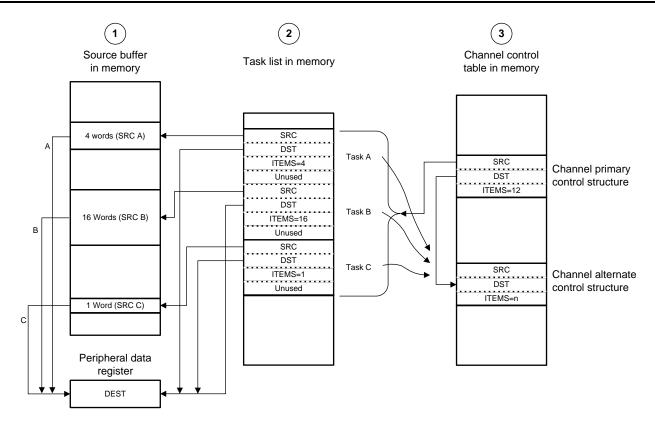

| 10-3. | Memory Scatter-Gather, Setup and Configuration                   | 295 |

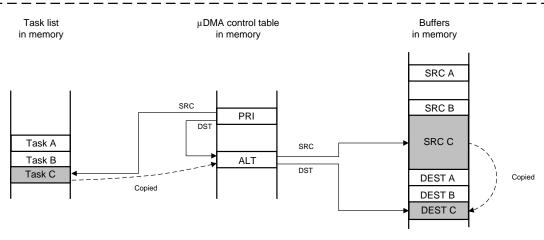

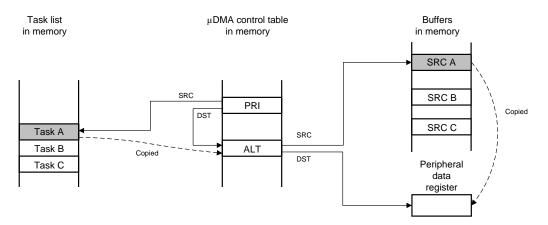

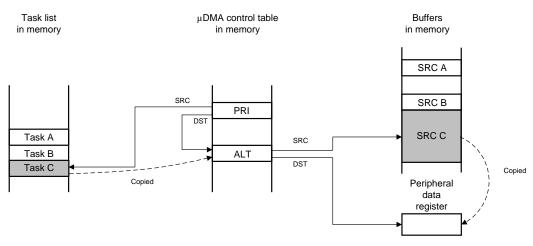

| 10-4. | Memory Scatter-Gather, µDMA Copy Sequence                        | 296 |

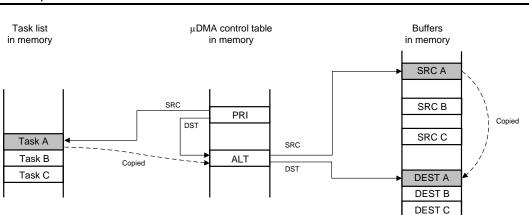

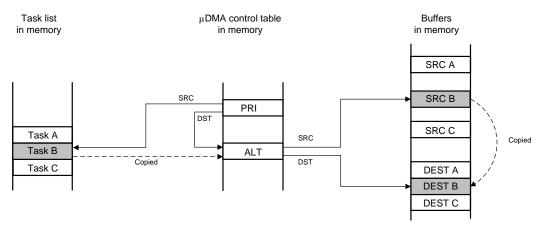

| 10-5. | Peripheral Scatter-Gather, Setup and Configuration               | 298 |

| 10-6. | Peripheral Scatter-Gather, µDMA Copy Sequence                    | 299 |

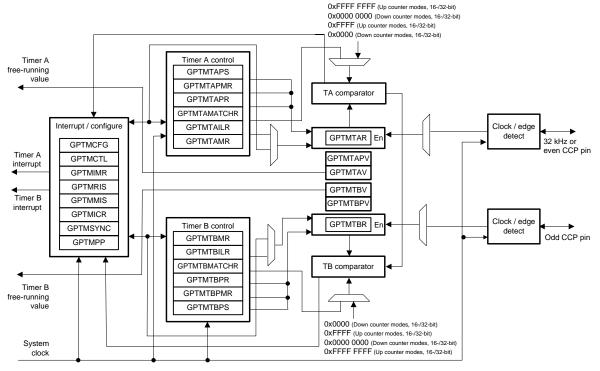

| 11-1. | GPTM Module Block Diagram                                        | 319 |

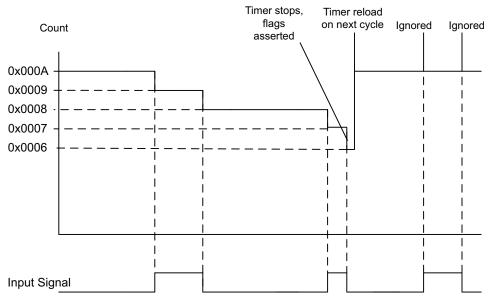

| 11-2. | Input Edge-Count Mode Example, Counting Down                     | 323 |

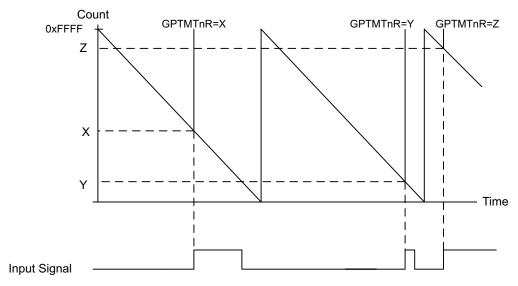

| 11-3. | Input Edge-Time Mode Example                                     | 324 |

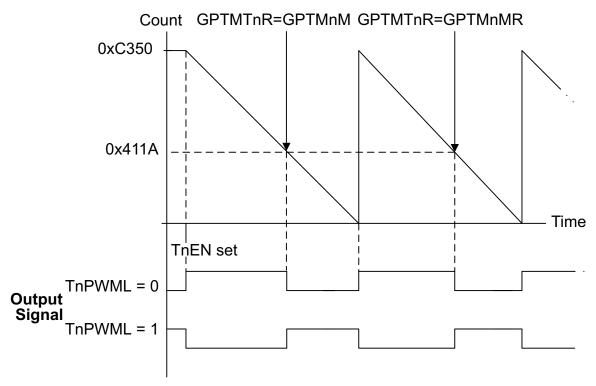

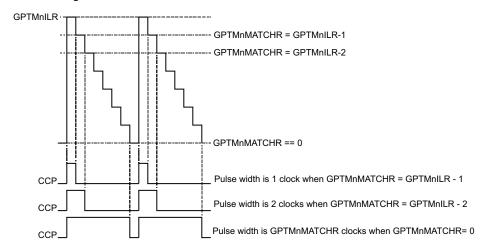

| 11-4. | 16-bit PWM Mode Example                                          | 326 |

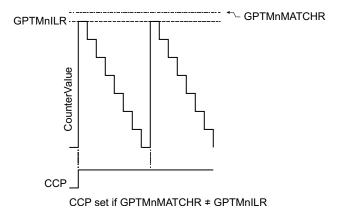

| 11-5. | CCP Output, GPTIMER_TnMATCHR > GPTIMER_TnILR                     | 326 |

| 11-6. | CCP Output, GPTIMER_TnMATCHR = GPTIMER_TnILR                     | 327 |

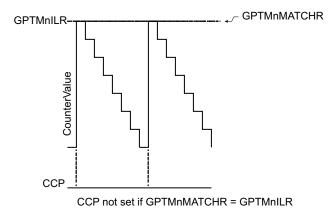

| 11-7. | CCP Output, GPTIMER_TnILR > GPTIMER_TnMATCHR                     | 327 |

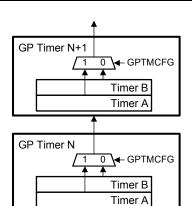

| 11-8. | Timer Daisy-Chain                                                | 328 |

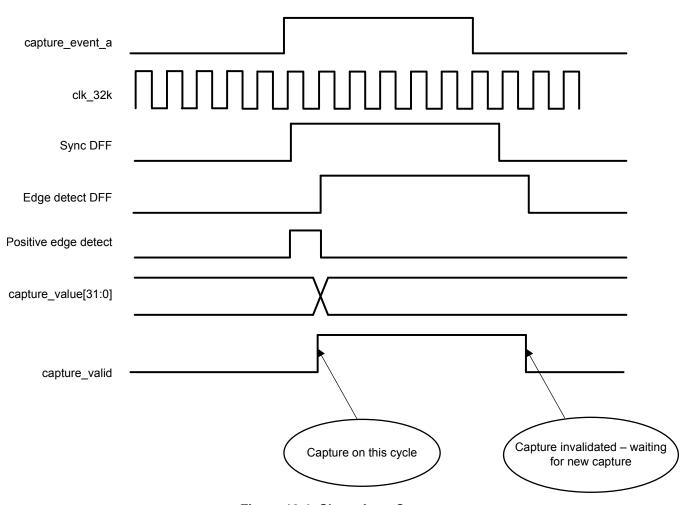

| 13-1. | Sleep timer Capture                                              | 364 |

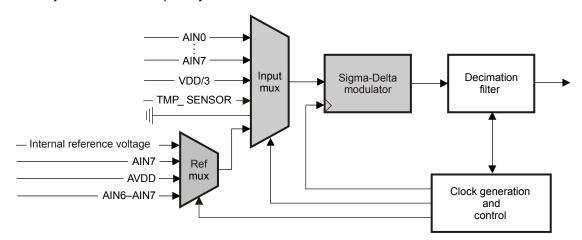

| 15-1. | ADC Block Diagram                                                | 374 |

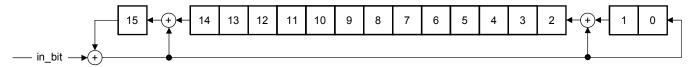

| 16-1. | Basic Structure of the RNG                                       | 382 |

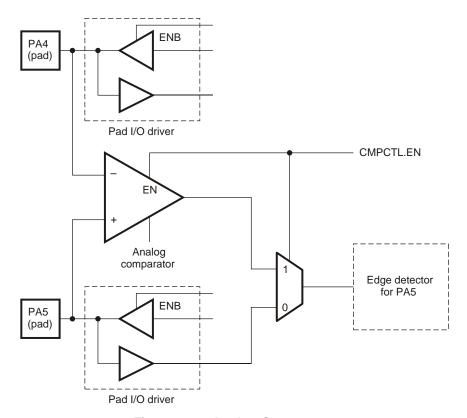

| 17-1. | Analog Comparator                                                | 386 |

| 18-1. | UART Module Block Diagram                                        | 390 |

| 18-2. | UART Character Frame                                             | 391 |

| 18-3. | LIN Message                                                      | 393 |

| 18-4. | LIN Synchronization Field                                        | 394 |

| 19-1. | SSI Module Block Diagram                                         | 416 |

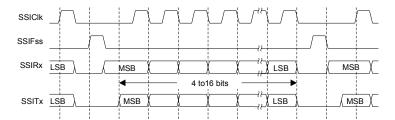

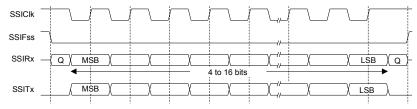

| 19-2. | TI Synchronous Serial Frame Format (Single Transfer)             | 419 |

| 19-3. | TI Synchronous Serial Frame Format (Continuous Transfer)         | 419 |

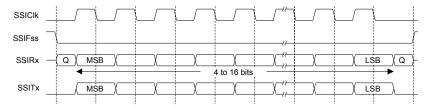

| 19-4. | Freescale SPI Format (Single Transfer) With SPO = 0 and SPH = 0  | 420 |

|       |                                                                  |     |

| 19-5.  | Freescale SPI Format (Continuous Transfer) With SPO = 0 and SPH = 0                        | 420 |

|--------|--------------------------------------------------------------------------------------------|-----|

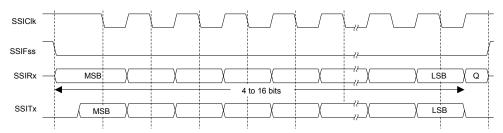

| 19-6.  | Freescale SPI Frame Format With SPO = 0 and SPH = 1                                        | 421 |

| 19-7.  | Freescale SPI Frame Format (Single Transfer) With SPO = 1 and SPH = 0                      | 421 |

| 19-8.  | Freescale SPI Frame Format (Continuous Transfer) With SPO = 1 and SPH = 0                  | 422 |

| 19-9.  | Freescale SPI Frame Format With SPO = 1 and SPH = 1                                        | 422 |

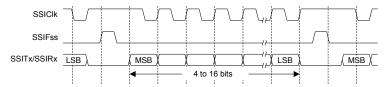

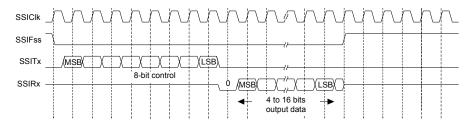

| 19-10. | MICROWIRE Frame Format (Single Frame)                                                      | 423 |

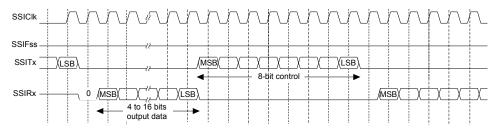

| 19-11. | MICROWIRE Frame Format (Continuous Transfer)                                               | 424 |

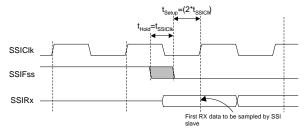

| 19-12. | MICROWIRE Frame Format, SSIFss Input Setup and Hold Requirements                           | 424 |

| 20-1.  | I <sup>2</sup> C Block Diagram                                                             | 435 |

| 20-2.  | I <sup>2</sup> C Bus Configuration                                                         | 436 |

| 20-3.  | Start and Stop Conditions                                                                  | 436 |

| 20-4.  | Complete Data Transfer With a 7-Bit Address                                                | 437 |

| 20-5.  | R/S Bit in First Byte                                                                      | 437 |

| 20-6.  | Data Validity During Bit Transfer on the I <sup>2</sup> C Bus                              | 437 |

| 20-7.  | Master Single TRANSMIT                                                                     | 440 |

| 20-8.  | Master Single RECEIVE                                                                      | 441 |

| 20-9.  | Master TRANSMIT With Repeated Start Condition                                              | 442 |

| 20-10. | Master RECEIVE With Repeated Start Condition                                               | 443 |

| 20-11. | Master RECEIVE With Repeated Start After TRANSMIT With Repeated Start Condition            | 444 |

| 20-12. | Master TRANSMIT With Repeated Start After RECEIVE With Repeated Start Condition            | 445 |

| 20-13. | Slave Command Sequence                                                                     | 446 |

| 21-1.  | USB Controller Block Diagram                                                               | 458 |

| 21-2.  | USB Interrupt Service Routine                                                              | 460 |

| 21-3.  | Endpoint 0 States                                                                          | 465 |