## Technical Article Generating Bias Current Networks with Arbitrary Magnitudes - Part Two

## Zachary Richards

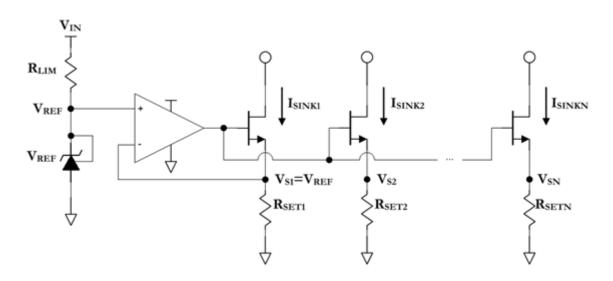

In the previous post in this series, an equation was derived to describe the ratio of the Nth  $R_{SET}$  resistor in Figure 1 below.

Figure 1. Current Sink Network

That equation, again, is as follows:

$$M_{RN} = M_{IN} x \left[ \left( 1 - \sqrt{M_{IN}} \right) x \left( 1 + \sqrt{\frac{2}{K_n x R_{SET1} x V_{REF}}} \right) + \sqrt{M_{IN}} \right]^{-1}$$

(1)

So, what can be said about Equation 1? First of all, for an  $M_{IN}$  ratio of 1, the corresponding  $M_{RN}$  ratio will also be 1, as would be expected. Second, for values of  $M_{IN}$  greater than 1, notice that the two terms of the denominator of Equation 1 take on different signs. This means that depending on certain physical quantities involved ( $K_n$ ,  $R_{SET1}$ ,  $V_{REF}$ ),  $M_{RN}$  can become arbitrarily large. Thus, this region should be avoided, instead favoring the  $M_{IN} \leq$  1 region; that is, by ensuring that  $I_{SINKN}$  is less than or equal to  $I_{SINK1}$  for all N.

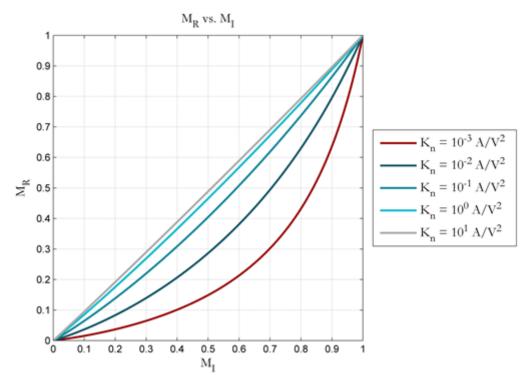

Notice that allowing the denominator of the root term in Equation 1 (the K<sub>n</sub>, R<sub>SET1</sub>, V<sub>REF</sub> product) to become large results in a 1:1 linear relationship between M<sub>RN</sub> and M<sub>IN</sub> in the limit. Ultimately, the range of usable values that V<sub>REF</sub> and R<sub>SET1</sub> can take on to increase this product are going to be limited by the headroom required for the sink; though it is worth noting that for a fixed I<sub>SINK1</sub> value, increasing V<sub>REF</sub> requires an increase in R<sub>SET1</sub> as well. The final variable in the product, K<sub>n</sub>, is the process transconductance of the MOSFET and can be maximized through device selection. The effect of K<sub>n</sub> on the linearity of the M<sub>RN</sub>, M<sub>IN</sub> relationship (across five decades of K<sub>n</sub> values) is illustrated in Figure 2 below.

The process transconductance is so named due to its dependence on carrier mobility, oxide permittivity, and oxide thickness ( $\mu$ ,  $\epsilon_{ox}$ ,  $t_{ox}$ )—all material and process properties:

$$K_n = k_n^{-1} x \frac{W}{L} = \mu_n x C_{ox} x \frac{W}{L} = \mu_n x \frac{E_{ox}}{t_{ox}} x \frac{W}{L}$$

$$\tag{2}$$

However, it is also dependent on the W/L ratio of the device, so in general larger devices will result in increasingly linear behavior in Equation 1. While most datasheets will not include  $K_n$ , it can be calculated from a common datasheet parameter, the forward transconductance, often listed as  $g_m$  or  $g_{FS}$ :

$$g_{m} = g_{FS} = \frac{\partial I_{Dn}}{\partial V_{GS}} = \frac{\partial}{\partial V_{GS}} \left( \frac{1}{2} x K_{n} x (V_{GS} - V_{T})^{2} \right) = K_{n} x (V_{GS} - V_{T})$$

(3)

Recall that the drain current equation for an NMOS operating in the saturation region is:

$$I_{Dn} = \frac{1}{2} \times K_n \times (V_{GS} - V_T)^2 \times (1 + \lambda \times V_{DS})$$

(4)

Neglecting channel length modulation and rewriting the terms of Equation 4:

$$V_{\rm GS} - V_T = \sqrt{\frac{2 \, x \, {\rm I}_{\rm D}}{{\rm K}_{\rm n}}} \tag{5}$$

This result can be substituted into Equation 3 and ultimately solved for K<sub>n</sub>:

$$g_{\rm m} = K_{\rm n} x \sqrt{\frac{2 x l_{\rm D}}{K_{\rm n}}} = \sqrt{2 x l_{\rm D} x K_{\rm n}}$$

(6)

$$K_n = \frac{g_m^2}{2 x I_D}$$

(7)

Generating Bias Current Networks with Arbitrary Magnitudes - Part Two

Thus, using Equation 7 it is possible to select optimal MOSFET devices for the bias network. Further, having obtained this value, it can be utilized in Equation 1 to calculate (more accurately) required  $R_{SETN}$  resistor values to produce desired  $I_{SINKN}$  currents.

It is important to note that Equation 1 tends to overestimate the  $R_{SETN}$  resistance in the  $M_{IN} \le 1$  region; that is, it results in currents that are lower than the desired value. However, the ideal transistor case ( $M_{IN}=M_{RN}$ ) will always underestimate the  $R_{SETN}$  resistance in this region. Thus, calculating these two values will ultimately bound the exact value required. Consider two randomly chosen NFETs, N-channel MOSFET A and N-channel MOSFET B, as represented in Table 1, which have listed  $g_{FS}$  values of 5.5A/V<sup>2</sup> (at  $I_D=9A$ ) and 15A/V<sup>2</sup> (at  $I_D=31A$ ), respectively. Suppose these are used to implement an  $M_{IN}$  ratio of ½; the corrected  $R_{SETN}$  and  $M_{RN}$  ratios are calculated using Equation 1 (along with some straightforward design values) in Table 1 below.

|                       | g <sub>FS</sub><br>(S) | I <sub>р</sub><br>(А) | K <sub>N</sub><br>(A/V <sup>2</sup> ) | V <sub>ref</sub><br>(V) | I <sub>SINK1</sub><br>(A) | I <sub>SINKN</sub><br>(A) | $\mathbf{M}_{\mathrm{IN}}$ | $R_{seti}$<br>( $\Omega$ ) | $R_{\text{setn}}$ $(\Omega)$ | $\mathbf{M}_{\mathrm{RN}}$ |

|-----------------------|------------------------|-----------------------|---------------------------------------|-------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------------------------------|----------------------------|

| N-channel<br>MOSFET A | 5.5                    | 9.0                   | 1.68                                  | 1.25                    | 1.0                       | 0.25                      | 0.25                       | 1.25                       | 7.18                         | 0.174                      |

| N-channel<br>MOSFET B | 15.0                   | 31.0                  | 3.63                                  | 1.25                    | 1.0                       | 0.25                      | 0.25                       | 1.25                       | 6.48                         | 0.193                      |

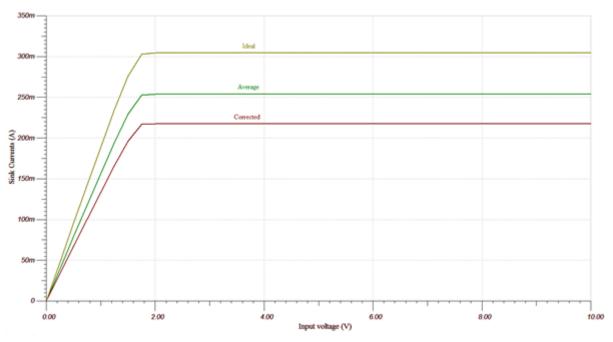

Using the conditions listed above for the N-channel MOSFET B, Figure 3 displays the results of a TINA-TI simulation of the circuit in Figure 1 implemented with  $R_{SETN}$  values calculated from the ideal case (5 $\Omega$  under these conditions), the corrected case (Equation 1), and the average of these two.

Figure 3. Sink Current vs. Drain Voltage for Ideal, Corrected, and Average R<sub>SETN</sub> Values

The results for simulations using both the N-channel MOSFET A and N-channel MOSFET B with the three R<sub>SETN</sub> values (as described above) are summarized along with corresponding percent error calculations in Table 2 below.

|                       | Ideal                                                      |                           |              | (                                                          | Correcte                  | d            | Average                                                    |                           |              |

|-----------------------|------------------------------------------------------------|---------------------------|--------------|------------------------------------------------------------|---------------------------|--------------|------------------------------------------------------------|---------------------------|--------------|

|                       | $\begin{array}{c} R_{\text{setn}} \\ (\Omega) \end{array}$ | I <sub>SINKN</sub><br>(A) | Error<br>(%) | $\begin{array}{c} R_{\text{setn}} \\ (\Omega) \end{array}$ | I <sub>SINKN</sub><br>(A) | Error<br>(%) | $\begin{array}{c} R_{\text{setn}} \\ (\Omega) \end{array}$ | I <sub>SINKN</sub><br>(A) | Error<br>(%) |

| N-channel<br>MOSFET A | 5.0                                                        | 0.304                     | 21.6         | 7.2                                                        | 0.218                     | -12.8        | 6.1                                                        | 0.254                     | 1.5          |

| N-channel<br>MOSFET B | 5.0                                                        | 0.283                     | 13.2         | <mark>6</mark> .5                                          | 0.221                     | -11.6        | 5.7                                                        | 0.248                     | -0.8         |

## Table 2. R<sub>SETN</sub> Calculation Methods and Resulting Accuracy

Ultimately a single feedback device can be used to derive a bias network of arbitrary values so long as certain conditions are met: particularly that the current in the primary feedback driven leg is the largest in the network, and the proper headroom is maintained in each leg. Thus, from a single voltage reference, a bias network is established.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated